### 4 Channel Digital Isolator with Integrated 0.65W Isolated DC/DC Power Module

#### DESCRIPTION

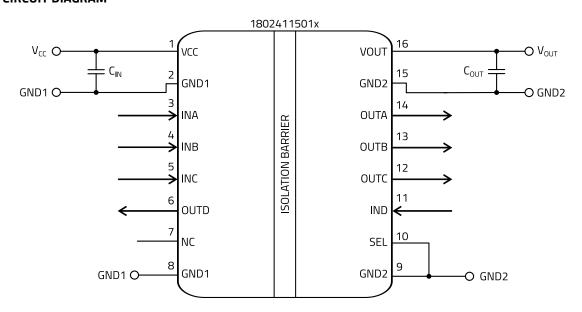

The CDIP 18024x15401x is a 4 channel digital isolator that includes an integrated isolated DC/DC power module.

A single external power supply is necessary to power both the primary side channels and the integrated isolated power supply. The integrated power supply generates the required isolated secondary supply voltage.

The integrated power module has integrated protection systems that guard against thermal overstress with thermal shutdown and protect against electrical damage using overcurrent, short-circuit and undervoltage circuitry.

The CDIP digital isolator ensures fast time to market and low development costs.

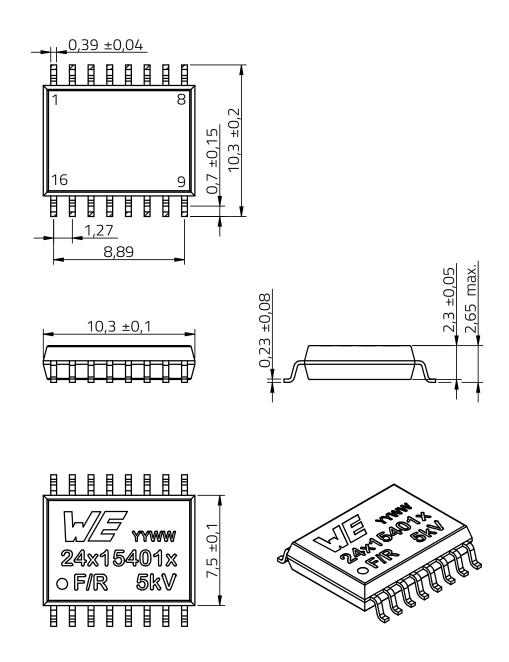

The digital isolator is available in an SOIC-16WB package (10.3 x 7.5 x 2.5)mm.

#### TYPICAL APPLICATIONS

- Communication bus isolation

- Motor control

- Battery management systems

- Solar inverters

- Test and measurement systems

- Programmable logic controller (PLC) interfaces

#### **FEATURES**

- 5kV<sub>RMS</sub> isolation for 60s

- Input voltage range: 3.15V to 5.5V

- User-selectable output voltage: 5V or 3.3V

- Data rate up to 100Mbps

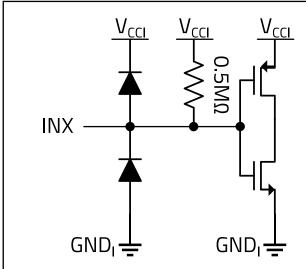

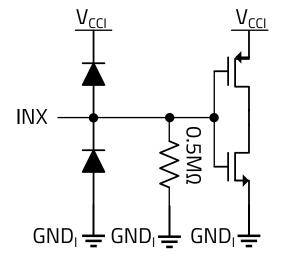

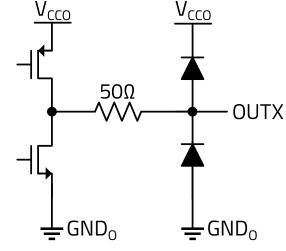

- $\pm 150$ kV/ $\mu$ s typ. CMTI

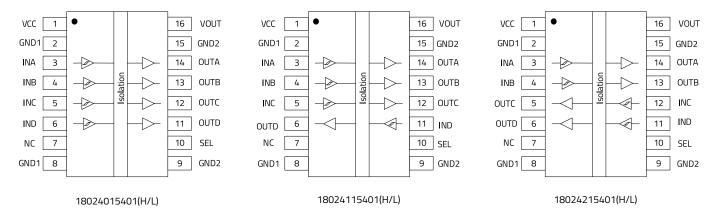

- Available channel configurations: 4/0, 3/1 and 2/2

- Default channel output status: high or low

- Low propagation delay: 10ns typ.

- Ambient temperature range: -40°C to 125°C

- RoHS and REACh compliant

- Complies with EN55032 (CISPR-32) class B conducted and radiated emissions standard

- UL1577 certified

- IEC 60747 pending

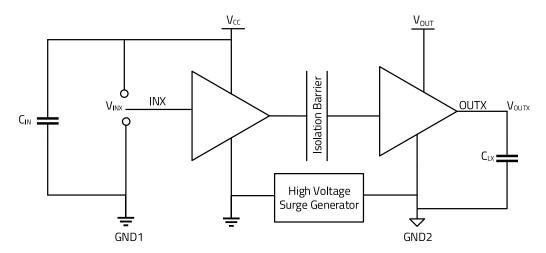

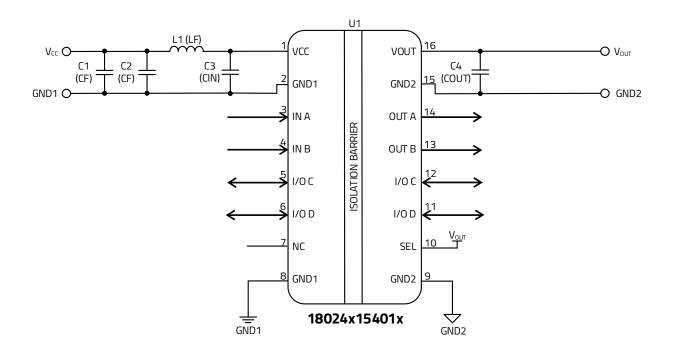

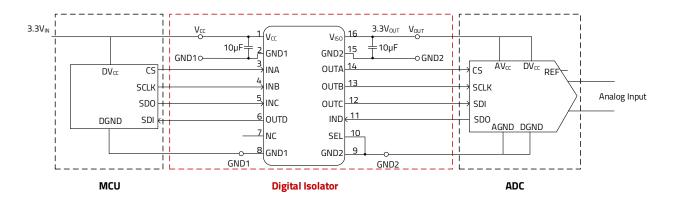

# **TYPICAL CIRCUIT DIAGRAM**

Data Sheet Version 1.1 © November 2023

# 18024x15401x

# **Digital Isolator**

**WPME-CDIP** - Capacitive Digital Isolator Powered

# **CONTENTS**

| 2 ORDERING INFORMATION  3 SALES INFORMATION  4 ABSOLUTE MAXIMUM RATINGS  5 OPERATING CONDITIONS  5 THERMAL SPECIFICATIONS  6 THERMAL SPECIFICATIONS  7 ELECTRICAL SPECIFICATIONS  8 ISOLATION SPECIFICATIONS  9 APPROVALS  10 ROHS, REACH  11 PACKAGE SPECIFICATIONS  12 NOTES  13 ISOLATION VOLTAGE  13.1 Isolation Voltage Testing  13.2 Dielectric Test Setup (High Pot Test)  13.3 Repeated High-Voltage Isolation Testing  14 TYPICAL PERFORMANCE CURVES  14.1 Radiated and Conducted Emissions (With EMI Input Filter)  14.1.1 Radiated Emissions ENDS503 (ISDRP-32) Class B Complaint Test Setup  14.1.2 Conducted Emissions ENDS5033 (ISDRP-32) Class B Complaint Test Setup  14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 De Performance Curves  14.2 1 Efficiency  14.2.3 Output Voltage Ripple  14.2.4 Thermal Derating  14.2.5 Propagation Delay vs. Ambient Temperature  14.2.6 Quiescent Current vs. Ambient Temperature  14.2.7 Supply Current vs. Ambient Temperature  14.2.8 Supply Current vs. Ambient Temperature  14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 SOft-Start  20.2 Overcurrent Protection (OCP) |   | 4                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------|

| 4 ABSOLUTE MAXIMUM RATINGS 5 OPERATING CONDITIONS 6 THERMAL SPECIFICATIONS 7 ELECTRICAL SPECIFICATIONS 8 ISOLATION SPECIFICATIONS 9 APPROVALS 10 ROHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dilectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x 14.2 Depriormance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Supply Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overurent Protection (OCP)                                                                                                                    |   | 5                                                        |

| 5 OPERATING CONDITIONS 6 THERMAL SPECIFICATIONS 7 ELECTRICAL SPECIFICATIONS 8 ISOLATION SPECIFICATIONS 9 APPROVALS 10 RoHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14.1 Typical Performance Curves 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.1 Radiated Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.1 Radiated and Conducted Emissions - 18024x15401x 14.2.1 Conducted Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.2.1 Efficiency 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                |   | 5                                                        |

| 6 THERMAL SPECIFICATIONS 7 ELECTRICAL SPECIFICATIONS 8 ISOLATION SPECIFICATIONS 9 APPROVALS 10 RoHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14.1 Padiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions ENS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x 14.2.1 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 OVECUTIVENT TOTOCCOP)                                                                                            |   | 6                                                        |

| 7 ELECTRICAL SPECIFICATIONS 8 ISOLATION SPECIFICATIONS 9 APPROVALS 10 RoHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated and Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x 14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                 |   | 6                                                        |

| 8 ISOLATION SPECIFICATIONS 9 APPROVALS 10 ROHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENISSO32 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions ENISSO32 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x 14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                       |   | 6                                                        |

| 9 APPROVALS 10 RoHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENIS5032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions ENIS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x154.01x 14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                     |   | 7                                                        |

| 9 APPROVALS 10 RoHS, REACh 11 PACKAGE SPECIFICATIONS 12 NOTES 13 ISOLATION VOLTAGE 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing 14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions ENIS5032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions ENIS5032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x154.01x 14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                     | • | 11                                                       |

| 10 RoHS, REACh  11 PACKAGE SPECIFICATIONS  12 NOTES  13 ISOLATION VOLTAGE  13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing  14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                    |   |                                                          |

| 11 PACKAGE SPECIFICATIONS  12 NOTES  13 ISOLATION VOLTAGE  13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing  14 TYPICAL PERFORMANCE CURVES  14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.9 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                     |   |                                                          |

| 13 ISOLATION VOLTAGE  13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing  14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Data Rate 14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                     |   |                                                          |

| 13. Isolation Voltage Testing 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing  14. TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x 14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.8 Supply Current vs. Ambient Temperature 14.2.9 High and Low Voltage Levels vs. Output Current 15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                       |   |                                                          |

| 13.1 Isolation Voltage Testing 13.2 Dielectric Test Setup (High Pot Test) 13.3 Repeated High-Voltage Isolation Testing  14 TYPICAL PERFORMANCE CURVES 14.1 Radiated and Conducted Emissions (With EMI Input Filter) 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup 14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 DC Performance Curves 14.2.1 Efficiency 14.2.2 Load Transients 14.2.3 Output Voltage Ripple 14.2.4 Thermal Derating 14.2.5 Propagation Delay vs. Ambient Temperature 14.2.6 Quiescent Current vs. Ambient Temperature 14.2.7 Supply Current vs. Ambient Temperature 14.2.8 Supply Current vs. Data Rate 14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE 16 IO DESCRIPTION 17 TEST SCHEMATICS 18 BLOCK DIAGRAM 19 CIRCUIT DESCRIPTION 20 PROTECTION FEATURES 20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                | 1 | 12                                                       |

| 14.1 Radiated and Conducted Emissions (With EMI Input Filter)  14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup  14.1.3 Radiated and Conducted Emissions = 18024x15401x  14.2 DC Performance Curves  14.2.1 Efficiency  14.2.2 Load Transients  14.2.3 Output Voltage Ripple  14.2.4 Thermal Derating  14.2.5 Propagation Delay vs. Ambient Temperature  14.2.6 Quiescent Current vs. Ambient Temperature  14.2.8 Supply Current vs. Ambient Temperature  14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start  20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 13<br>13                                                 |

| 14.1.3 Radiated and Conducted Emissions - 18024x15401x  14.2 DC Performance Curves  14.2.1 Efficiency  14.2.2 Load Transients  14.2.3 Output Voltage Ripple  14.2.4 Thermal Derating  14.2.5 Propagation Delay vs. Ambient Temperature  14.2.6 Quiescent Current vs. Ambient Temperature  14.2.7 Supply Current vs. Ambient Temperature  14.2.8 Supply Current vs. Data Rate  14.2.9 High and Low Voltage Levels vs. Output Current  15 TRUTH TABLE  16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start  20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                          |

| 16 IO DESCRIPTION  17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 14<br>15<br>21<br>21<br>23<br>24<br>26<br>28<br>30<br>32 |

| 17 TEST SCHEMATICS  18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 35                                                       |

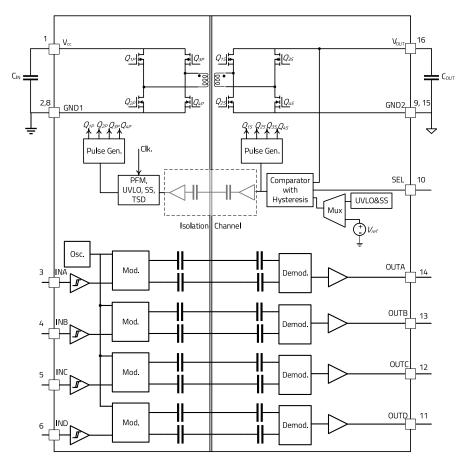

| 18 BLOCK DIAGRAM  19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start 20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 | 35                                                       |

| 19 CIRCUIT DESCRIPTION  20 PROTECTION FEATURES  20.1 Soft-Start  20.2 Overcurrent Protection (OCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 36                                                       |

| 20 PROTECTION FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 37                                                       |

| 20.1 Soft-Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 37                                                       |

| 20.3 Short-Circuit Protection (SCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 | 38<br>38                                                 |

# 18024x15401x

# **Digital Isolator**

# **WPME-CDIP** - Capacitive Digital Isolator Powered

|    | 20.4 Input/Output Undervoltage Lockout (UVLO)                                     |          |

|----|-----------------------------------------------------------------------------------|----------|

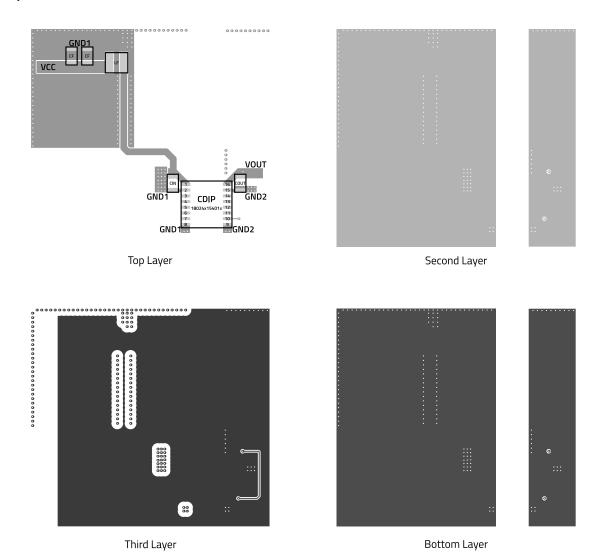

| 21 | DESIGN EXAMPLE  21.1 Layout  21.2 Schematic  21.3 Bill of Materials               | 41<br>42 |

| 22 | TYPICAL APPLICATION                                                               | 43       |

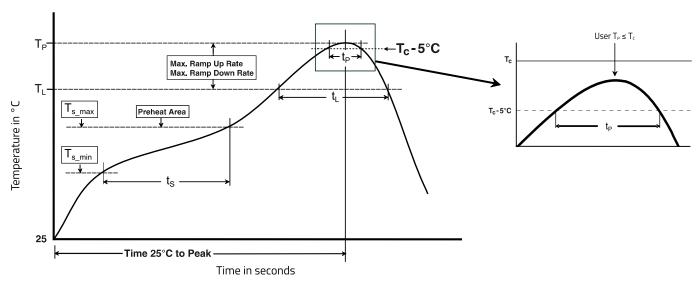

| 23 | HANDLING RECOMMENDATIONS                                                          |          |

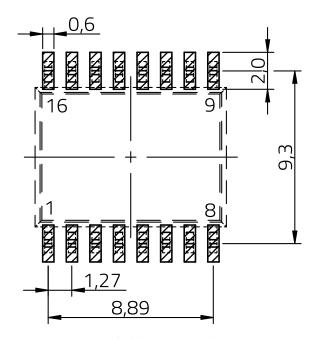

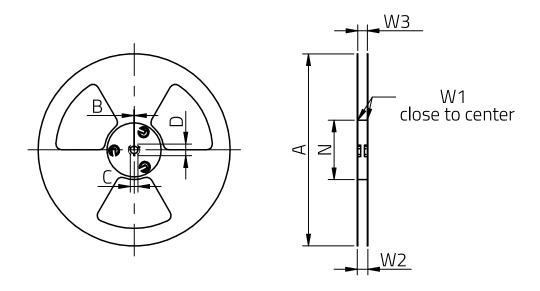

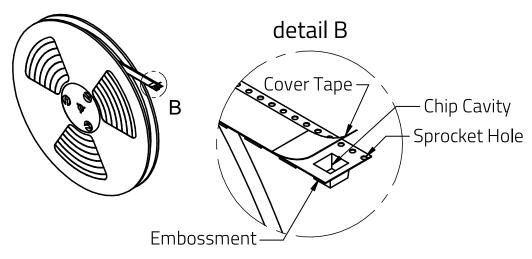

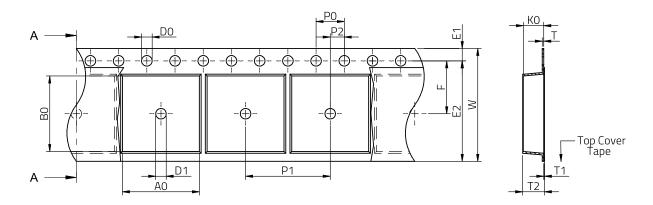

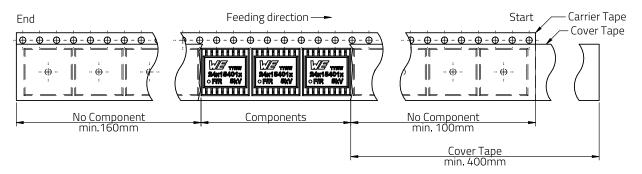

| 24 | PHYSICAL DIMENSIONS  24.1 Component  24.2 Recommended Landpattern  24.3 Packaging | 45<br>46 |

| 25 | DOCUMENT HISTORY                                                                  | 49       |

| 26 | LIST OF FIGURES                                                                   | 50       |

| 27 | LIST OF TABLES                                                                    | 52       |

| 28 | CAUTIONS AND WARNINGS                                                             | 53       |

| 29 | IMPORTANT NOTES                                                                   | 54       |

### 1 PINOUT

Figure 1: Pinout.

Table 1: Marking description.

| MARKING   | DESCRIPTION                             |

|-----------|-----------------------------------------|

| WE        | Würth Elektronik eiSos<br>GmbH & Co. KG |

| YYWW      | Year and calendar week                  |

| 24x15401x | Order code                              |

| F/R       | Number of forward/reverse channels      |

| 5kV       | 5kV isolation voltage                   |

Figure 2: Marking.

Table 2: Pin description.

| SYMBOL   | NUMBER | TYPE  | DESCRIPTION                                                                                           |

|----------|--------|-------|-------------------------------------------------------------------------------------------------------|

| VCC      | 1      | Power | Integrated power module voltage input.                                                                |

| GND1     | 2      | Power | Primary side ground connection.                                                                       |

| INA      | 3      | 1/0   | Digital input A.                                                                                      |

| INB      | 4      | 1/0   | Digital input B.                                                                                      |

| INC/OUTC | 5      | 1/0   | Digital input/output C.                                                                               |

| IND/OUTD | 6      | 1/0   | Digital input/output D.                                                                               |

| NC       | 7      | NC    | Not internally connected.                                                                             |

| GND1     | 8      | Power | Primary side ground connection.                                                                       |

| GND2     | 9      | Power | Secondary side ground connection.                                                                     |

| SEL      | 10     | Input | Output voltage selection pin. Connect to VOUT pin for 5V. Connect to GND2 for 3.3V.                   |

| OUTD/IND | 11     | 1/0   | Digital input/output D.                                                                               |

| OUTC/INC | 12     | 1/0   | Digital input/output C.                                                                               |

| OUTB     | 13     | 1/0   | Digital output B.                                                                                     |

| OUTA     | 14     | 1/0   | Digital output A.                                                                                     |

| GND2     | 15     | Power | Secondary side ground connection.                                                                     |

| VOUT     | 16     | Power | Integrated power module voltage output. Either 5V or 3.3V, depending on the state applied to SEL pin. |

## **2 ORDERING INFORMATION**

Table 3: Ordering information.

| ORDER CODE   | SPECIFICATIONS                     | PACKAGE    | PACKAGING UNIT         |

|--------------|------------------------------------|------------|------------------------|

| 18024015401H | 4 forward, 0 reverse, default high |            |                        |

| 18024015401L | 4 forward, 0 reverse, default low  |            |                        |

| 18024115401H | 3 forward, 1 reverse, default high | SOIC-16WB  | 13" Reel (1000 pieces) |

| 18024115401L | 3 forward, 1 reverse, default low  | JOIC TOWN  | 13 Reel (1000 pieces)  |

| 18024215401H | 2 forward, 2 reverse, default high |            |                        |

| 18024215401L | 2 forward, 2 reverse, default low  |            |                        |

| 18824x15401x | _                                  | Eval Board | 1 piece                |

### **3 SALES INFORMATION**

### **SALES CONTACT**

Würth Elektronik eiSos GmbH & Co. KG EMC and Inductive Solutions Max-Eyth-Str. 1 74638 Waldenburg

Germany

Tel. +49 (0) 7942 945 0

www.we-online.com/digitalisolators

Technical support: powermodules@we-online.com

#### **4 ABSOLUTE MAXIMUM RATINGS**

#### **Caution:**

Exceeding the listed absolute maximum ratings may affect the device negatively and may cause permanent damage.

Table 4: Absolute maximum ratings.

| SYMBOL               | PARAMETER                                    | LIN                | UNIT                                 |      |

|----------------------|----------------------------------------------|--------------------|--------------------------------------|------|

| STWIBOL              | PARAMETER                                    | MIN <sup>(1)</sup> | MAX <sup>(1)</sup>                   | ONIT |

| VCC                  | Supply pin voltage                           | -0.5               | 6                                    | V    |

| VOUT                 | Isolated supply output voltage pin           | -0.5               | 6                                    | V    |

| INX, OUTX            | Voltage at INX, OUTX, SEL pins               |                    | V <sub>CC</sub> + 0.5 <sup>(2)</sup> | V    |

| I <sub>OUTX</sub>    | Channel output current                       | -20                | 20                                   | mA   |

| $T_{\text{storage}}$ | Assembled, non-operating storage temperature |                    | 150                                  | °C   |

| $V_{ESD}$            | ESD voltage (HBM) <sup>(4)</sup>             | -6                 | 6                                    | kV   |

| $V_{ESD}$            | ESD voltage (CDM) <sup>(4)</sup>             | -2                 | 2                                    | kV   |

#### **5 OPERATING CONDITIONS**

Operating conditions are conditions under which the device is intended to be functional. All values are either referenced to GND1 or GND2.

MIN and MAX limits are valid for the recommended ambient temperature range of -40°C to 125°C.

Table 5: Operating conditions.

| SYMBOL                | PARAMETER                                                 | MIN <sup>(1)</sup> | TYP <sup>(3)</sup> | MAX <sup>(1)</sup> | UNIT |

|-----------------------|-----------------------------------------------------------|--------------------|--------------------|--------------------|------|

| V <sub>CC</sub>       | V <sub>CC</sub> Supply voltage                            |                    | _                  | 5.5                | V    |

| $V_{INX_{-H}}$        | Logic input high threshold                                | 2.0                | _                  | _                  | V    |

| $V_{INX_{L}}$         | Logic input low threshold                                 | _                  | _                  | 0.8                | V    |

| l <sub>он</sub>       | High-level channel output current V <sub>OUT</sub> = 5V   | -4                 | _                  | _                  | mA   |

| ОН                    | High-level channel output current V <sub>OUT</sub> = 3.3V | -2                 | _                  | _                  | mA   |

| lo                    | Low-level channel output current V <sub>OUT</sub> = 5V    | _                  | _                  | 4                  | mA   |

| I <sub>OL</sub>       | Low-level channel output current V <sub>OUT</sub> = 3.3V  | _                  | _                  | 2                  | mA   |

| DR                    | Data rate                                                 | 0                  | _                  | 100                | Mbps |

| PW Signal pulse width |                                                           | 5                  | _                  | _                  | ns   |

| Ta                    | Ambient temperature range                                 | -40                | _                  | 125                | °C   |

### **6 THERMAL SPECIFICATIONS**

#### **Caution:**

Exceeding the listed absolute maximum ratings may affect the device negatively and may cause permanent damage.

Table 6: Thermal specifications.

| SYMBOL         | PARAMETER                                                | TEST CONDITIONS                                                                                                                                       | MIN <sup>(1)</sup> | TYP <sup>(3)</sup> | MAX <sup>(1)</sup> | UNIT |

|----------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| $\Theta_{JA}$  | Junction-to-ambient<br>thermal resistance <sup>(5)</sup> |                                                                                                                                                       | _                  | 68.5               | _                  | °C/W |

| P <sub>D</sub> | Maximum power dissipation                                | V <sub>CC</sub> =5.5V, V <sub>OUT</sub> =5V,<br>I <sub>OUT</sub> =0.13A, 50% duty cycle<br>square signal on all<br>channels with C <sub>L</sub> =15pF | _                  | _                  | 1                  | W    |

Data Sheet Version 1.1 © November 2023

### 7 ELECTRICAL SPECIFICATIONS

#### Caution:

MIN and MAX limits are valid for the recommended ambient temperature range of -40 °C to 125 °C. Typical values represent statistically the utmost probable values at the following conditions:  $V_{CC} = 5V$  or 3.3V,  $T_A = 25$  °C, unless otherwise noted.

Table 7: Electrical specifications part 1.

| SYMBOL                              | PARAMETER                                                      | TEST CONDITIONS                                                                           | MIN <sup>(1)</sup> | TYP <sup>(3)</sup>     | MAX <sup>(1)</sup> | UNIT  |

|-------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|------------------------|--------------------|-------|

|                                     | Integrate                                                      | ed Isolated Power Supply Output Vol                                                       | tage               |                        |                    |       |

|                                     | Integrated isolated supply                                     | V <sub>SEL</sub> = OV                                                                     | 3.13               | 3.3                    | 3.47               | V     |

|                                     | regulated output voltage                                       | $V_{CC} = 5V, V_{SEL} = V_{OUT}$                                                          | 4.75               | 5                      | 5.25               | V     |

| $V_{\text{OUT}}$                    | DC line regulation                                             | $V_{CC} = 4.5V \text{ to } 5.5V \text{ or } 3V \text{ to } 3.6V,$ $I_{OUT} = 50\text{mA}$ |                    | 2                      | _                  | mV/V  |

|                                     | DC load regulation                                             | $V_{CC} = 5V$ , $I_{OUT} = 0A$ to 0.13A                                                   | _                  | 1                      | _                  | %     |

|                                     | Output voltage ripple                                          |                                                                                           | _                  | 50                     |                    | mV    |

|                                     | Undervoltage lockout falling threshold                         |                                                                                           | 2.0                | 2.35                   | _                  | V     |

| $V_{\text{UVLO}}$                   | Undervoltage lockout rising threshold                          |                                                                                           | _                  | 2.75                   | 3.05               | V     |

|                                     | Undervoltage lockout<br>hysteresis                             |                                                                                           |                    | 400                    | _                  | mV    |

| 1                                   | Output current <sup>(7)</sup>                                  | $V_{CC} = 5V$                                                                             | _                  | 0.13                   |                    | А     |

| I <sub>OUT</sub>                    | Output current                                                 | V <sub>CC</sub> = 3.3V                                                                    | _                  | 0.075                  | _                  | Α     |

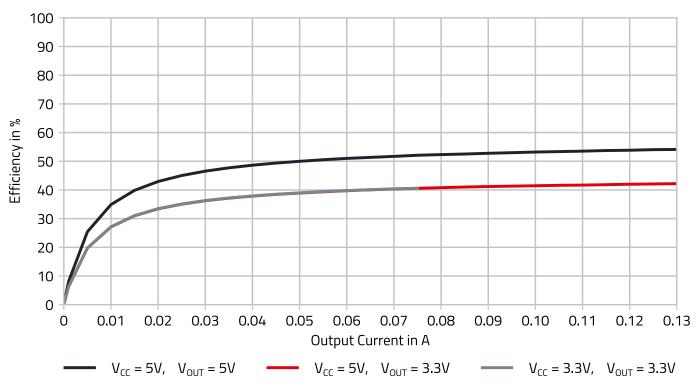

| η                                   | Efficiency                                                     | $V_{CC} = 5V, V_{OUT} = 5V, I_{OUT} = 0.13A$                                              |                    | 54                     |                    | %     |

|                                     |                                                                | Channel Characteristics                                                                   |                    |                        |                    |       |

| I <sub>IH</sub>                     | High-level input leakage current                               | $V_{INX} = V_{CC} \text{ or } V_{OUT}$                                                    | _                  | _                      | 20                 | μА    |

| I <sub>IL</sub>                     | Low-level input leakage current                                | V <sub>INX</sub> = OV                                                                     | -20                | _                      | _                  | μΑ    |

| $V_{OH}$                            | High-level output voltage                                      | V <sub>INX</sub> = V <sub>CC</sub> or V <sub>OUT</sub>                                    |                    | V <sub>INX</sub> - 0.2 | _                  | V     |

| V <sub>OL</sub>                     | Low-level output voltage                                       | V <sub>INX</sub> = OV                                                                     | T -                | 0.2                    | _                  | V     |

| CMTI                                | Common-mode transient immunity                                 | $V_{INX} = V_{CC}$ or OV, $V_{CM} = 1500V$                                                |                    | 150                    | _                  | kV/µs |

|                                     |                                                                | Timing Characteristics                                                                    |                    |                        |                    |       |

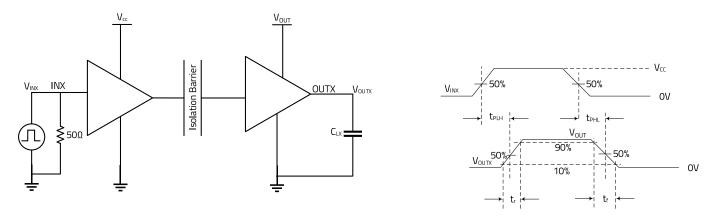

| t <sub>r</sub>                      | Output signal rise time                                        | 10% to 90% of V <sub>OUTX</sub>                                                           | T —                | 2.5                    | 4.0                | ns    |

| t <sub>f</sub>                      | Output signal fall time                                        | 90% to 10% of V <sub>OUTX</sub>                                                           | T -                | 2.5                    | 4.0                | ns    |

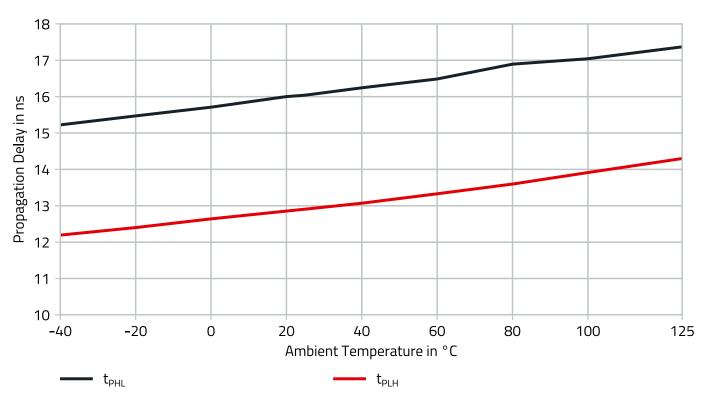

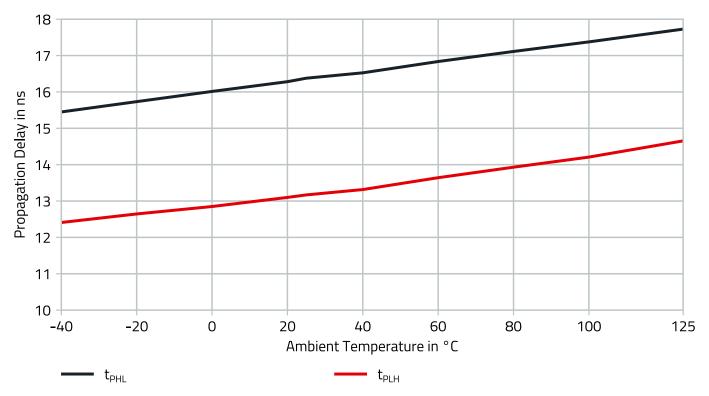

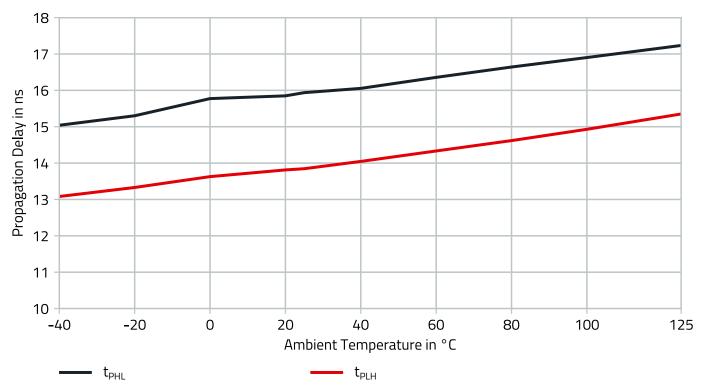

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                         | 50% of V <sub>INX</sub> to 50% of V <sub>OUTX</sub>                                       | _                  | 10                     | 20                 | ns    |

| PWD                                 | Pulse width distortion<br> t <sub>PLH</sub> - t <sub>PHL</sub> |                                                                                           |                    | 0.2                    | 4.5                | ns    |

| t <sub>sk(C-C)</sub>                | Channel-to-channel output skew time                            |                                                                                           |                    | 0.4                    | 2.5                | ns    |

| t <sub>SK(P-P)</sub>                | Part-to-part output skew time                                  |                                                                                           |                    | 2.0                    | 4.5                | ns    |

Parameters indicated in electrical specifications part 1 are applicable across all part numbers with all input/output conditions unless otherwise specified.

Data Sheet Version 1.1 © November 2023

Table 8: Electrical specifications part 2.

| SYMBOL           | PARAMETER                                                      | TEST CONDITIONS                                                            | MIN <sup>(1)</sup> | TYP <sup>(3)</sup> | MAX <sup>(1)</sup> | UNIT |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

|                  | 180                                                            | 024015401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 5V                  |                    |                    |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                         | _                  | 11                 | _                  | mΑ   |

|                  |                                                                | V <sub>INX</sub> ≠ channel default                                         | _                  | 15.5               | _                  | mA   |

| l <sub>cc</sub>  | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 13.6               | _                  | mA   |

| יננ              | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty<br>cycle square wave input signal  | _                  | 17.9               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal    | _                  | 58.6               | _                  | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    | _                  | 80                 | _                  | mA   |

|                  | 180                                                            | 024115401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 5V                  |                    | •                  |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                         | l –                | 10                 | _                  | mΑ   |

|                  | Integrated isolated power supply input current <sup>(8)</sup>  | V <sub>INX</sub> ≠ channel default                                         | _                  | 15                 | _                  | mΑ   |

| I <sub>CC</sub>  |                                                                | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 13.7               | _                  | mA   |

| יננ              |                                                                | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal     | _                  | 17.8               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal    | _                  | 56.2               | _                  | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    | _                  | 90                 | _                  | mA   |

|                  | 180                                                            | 024215401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 5V                  |                    |                    |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                         | _                  | 9.8                | _                  | mΑ   |

|                  |                                                                | V <sub>INX</sub> ≠ channel default                                         | _                  | 15.9               | _                  | mΑ   |

| l <sub>cc</sub>  | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 13.6               | _                  | mA   |

| יננ              | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal     | _                  | 17.2               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty<br>cycle square wave input signal |                    | 50.3               |                    | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    | _                  | 100                |                    | mA   |

Table 9: Electrical specifications part 3.

| SYMBOL                                                        | PARAMETER                                                      | TEST CONDITIONS                                                            | MIN <sup>(1)</sup> | TYP <sup>(3)</sup> | MAX <sup>(1)</sup> | UNIT |  |  |

|---------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|--|--|

| 18024015401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 3.3V |                                                                |                                                                            |                    |                    |                    |      |  |  |

|                                                               |                                                                | V <sub>INX</sub> = channel default                                         | _                  | 9.3                | _                  | mΑ   |  |  |

|                                                               |                                                                | V <sub>INX</sub> ≠ channel default                                         | _                  | 13.7               | _                  | mΑ   |  |  |

| l <sub>cc</sub>                                               | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 11.7               | _                  | mA   |  |  |

| יננ                                                           | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal     | _                  | 14.3               | _                  | mA   |  |  |

|                                                               |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal    | _                  | 36                 | _                  | mA   |  |  |

| I <sub>OUT</sub>                                              | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    | _                  | 80                 | _                  | mA   |  |  |

|                                                               | 1802                                                           | 24115401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 3.3V                 |                    |                    |                    |      |  |  |

|                                                               | Integrated isolated power supply input current <sup>(8)</sup>  | V <sub>INX</sub> = channel default                                         | _                  | 8.6                | _                  | mΑ   |  |  |

|                                                               |                                                                | V <sub>INX</sub> ≠ channel default                                         | _                  | 13.2               |                    | mΑ   |  |  |

| I <sub>CC</sub>                                               |                                                                | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 11.8               | _                  | mA   |  |  |

| יננ                                                           |                                                                | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal     | _                  | 14.4               | _                  | mA   |  |  |

|                                                               |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty<br>cycle square wave input signal | _                  | 40                 | _                  | mA   |  |  |

| I <sub>OUT</sub>                                              | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    | _                  | 90                 | _                  | mA   |  |  |

|                                                               | 1802                                                           | 24215401x V <sub>CC</sub> = 5V and V <sub>OUT</sub> = 3.3V                 |                    |                    |                    |      |  |  |

|                                                               |                                                                | V <sub>INX</sub> = channel default                                         | _                  | 8.6                | _                  | mA   |  |  |

|                                                               |                                                                | V <sub>INX</sub> ≠ channel default                                         | _                  | 14                 | _                  | mA   |  |  |

| l <sub>cc</sub>                                               | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal      | _                  | 11.9               | _                  | mA   |  |  |

| יננ                                                           | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal     |                    | 14.4               |                    | mA   |  |  |

|                                                               |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty<br>cycle square wave input signal | _                  | 40.5               | _                  | mA   |  |  |

| I <sub>OUT</sub>                                              | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                    |                    | 100                | _                  | mA   |  |  |

Table 10: Electrical specifications part 4.

| SYMBOL           | PARAMETER                                                      | TEST CONDITIONS                                                         | MIN <sup>(1)</sup> | TYP <sup>(3)</sup> | MAX <sup>(1)</sup> | UNIT |

|------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

|                  | 1802                                                           | $4015401x V_{CC} = 3.3V \text{ and } V_{OUT} = 3.3V$                    | I                  |                    |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                      | _                  | 10.7               | _                  | mΑ   |

|                  |                                                                | V <sub>INX</sub> ≠ channel default                                      | _                  | 15.5               | _                  | mA   |

| I <sub>cc</sub>  | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal   | _                  | 13.3               | _                  | mA   |

| יננ              | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal  | _                  | 16.3               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal | _                  | 46.7               | _                  | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                 | _                  | 45                 | _                  | mA   |

|                  | 1802                                                           | 4115401x V <sub>CC</sub> = 3.3V and V <sub>OUT</sub> = 3.3V             | i                  |                    |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                      | _                  | 10                 | _                  | mΑ   |

|                  | Integrated isolated power supply input current <sup>(8)</sup>  | V <sub>INX</sub> ≠ channel default                                      | _                  | 15.3               | _                  | mA   |

| I <sub>cc</sub>  |                                                                | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal   | _                  | 13.3               | _                  | mA   |

| יננ              |                                                                | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal  | _                  | 16.1               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal | _                  | 44.4               | _                  | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                 | _                  | 50                 | _                  | mA   |

|                  | 1802                                                           | 4215401x V <sub>CC</sub> = 3.3V and V <sub>OUT</sub> = 3.3V             | i                  | •                  |                    |      |

|                  |                                                                | V <sub>INX</sub> = channel default                                      | -                  | 9.7                | _                  | mA   |

|                  |                                                                | V <sub>INX</sub> ≠ channel default                                      | _                  | 15.7               | _                  | mA   |

| Icc              | Integrated isolated power                                      | 1Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal   | _                  | 13.3               | _                  | mA   |

| יננ              | supply input current <sup>(8)</sup>                            | 10Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal  | _                  | 15.8               | _                  | mA   |

|                  |                                                                | 100Mbps, C <sub>L</sub> = 15pF, 50% duty cycle square wave input signal | _                  | 41.5               | _                  | mA   |

| I <sub>OUT</sub> | Integrated isolated power supply output current <sup>(8)</sup> | 100Mbps                                                                 |                    | 55                 |                    | mA   |

# **8 ISOLATION SPECIFICATIONS**

Table 11: Isolation specification table.

| SYMBOL                | PARAMETER                           | TEST CONDITIONS                                                                                                                             | TYP <sup>(3)</sup> | UNIT      |  |

|-----------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|--|

| CLR                   | External clearance                  | Shortest distance through air between terminals                                                                                             | 8                  | mm        |  |

| CPG                   | External creepage                   | Shortest distance across package surface between terminals                                                                                  | 8                  | mm        |  |

| DTI                   | Distance through the insulation     | Minimum internal clearance                                                                                                                  | 19                 | μm        |  |

| СТІ                   | Comparative tracking index          | DIN EN 60112 (VDE 0303-11); IEC<br>60112                                                                                                    | >600               | V         |  |

|                       | IEC 60664-1 overvoltage category    | Rated mains voltage ≤300 V <sub>RMS</sub>                                                                                                   | I-IV               |           |  |

|                       |                                     | Rated mains voltage ≤400 V <sub>RMS</sub>                                                                                                   | I-IV               |           |  |

|                       |                                     | Rated mains voltage ≤600 V <sub>RMS</sub>                                                                                                   | I-IV               |           |  |

|                       |                                     | Rated mains voltage ≤1000 V <sub>RMS</sub>                                                                                                  | 1-111              |           |  |

| UL1577                |                                     |                                                                                                                                             |                    |           |  |

| V <sub>ISO(max)</sub> | Max. withstanding isolation voltage | V <sub>TEST</sub> = V <sub>ISO</sub> , t = 60s (qualification),<br>V <sub>TEST</sub> = 1.2 x V <sub>ISO</sub> , t = 1s (100%<br>production) | 5000               | $V_{RMS}$ |  |

#### 9 APPROVALS

Table 12: Approvals.

| SYMBOL          | STANDARD                         | DESCRIPTION                                                                                                                           |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| c <b>SU</b> °us | UL 1577, 5 <sup>th</sup> Edition | Nonoptical Isolating Devices – Component<br>UL Category: FPPT2 & FPPT8<br>UL File No: E535458<br>Applicable for altitudes up to 2000m |

## 10 RoHS, REACh

Table 13: RoHS, REACh.

RoHS directive

REACh directive

COMPLIANT

ROHS&REACH

WÜRTH ELEKTRONIK

Directive 2011/65/EU of the European Parliament and the Council of June 8th, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

Directive 1907/2006/EU of the European Parliament and the Council of June 1st, 2007 regarding the Registration, Evaluation, Authorization and Restriction of Chemicals (REACh).

#### 11 PACKAGE SPECIFICATIONS

Table 14: Package specifications.

| ITEM        | PARAMETER | TYP <sup>(3)</sup> | UNIT |

|-------------|-----------|--------------------|------|

| Lead finish | _         | Matte Sn           | _    |

| Weight      | _         | 0.42               | g    |

#### 12 NOTES

- (1) Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods.

- (2) This value must never exceed 6V.

- (3) Typical numbers are valid at 25°C ambient temperature and represent statistically the utmost probability assuming the Gaussian distribution.

- (4) The human body model is a 100pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. Test method is per JESD-22-114. The charged device model test method is per JESD22-C101.

- (5) Measured without heatsink, still air. (0 20LFM / 0 0.1m/s) Test PCB 80mm x 80mm horizontal orientation 35μm copper on top and bottom.

- (6) 100% final production tested value. The qualified isolation voltage value is 5kV<sub>RMS</sub>. For detailed isolation characteristics see the isolation specification table (Isolation specification table).

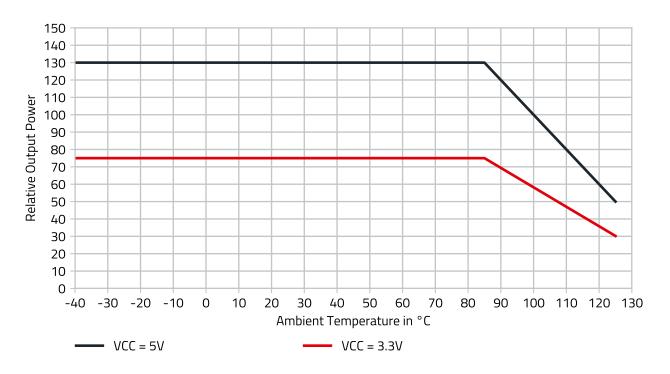

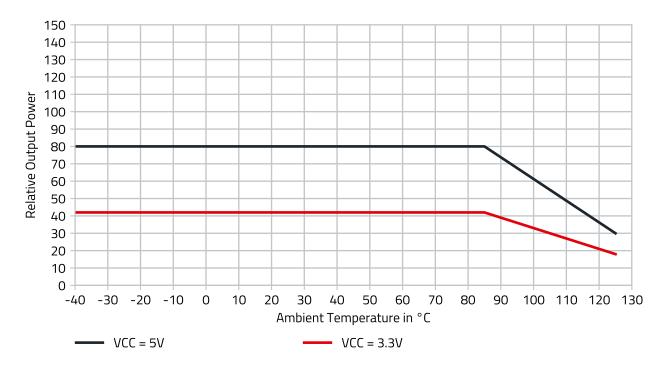

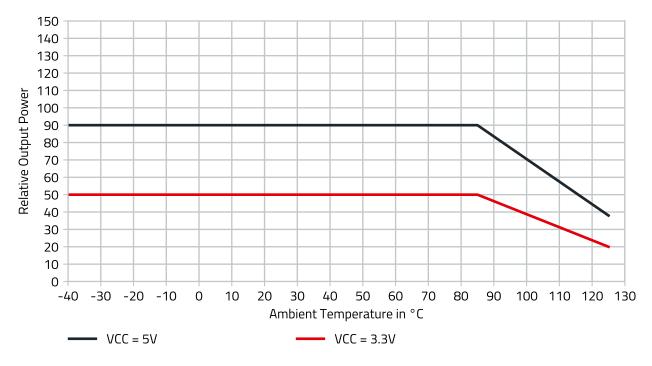

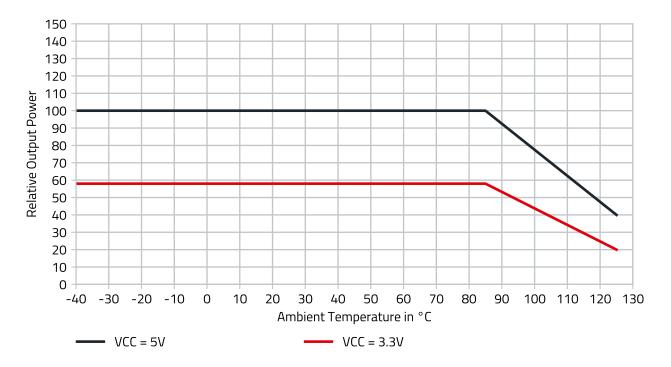

- (7) Depending on ambient temperature, see thermal derating diagram (Thermal Derating).

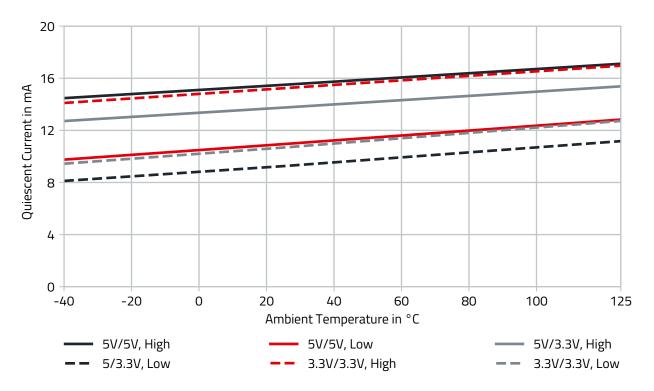

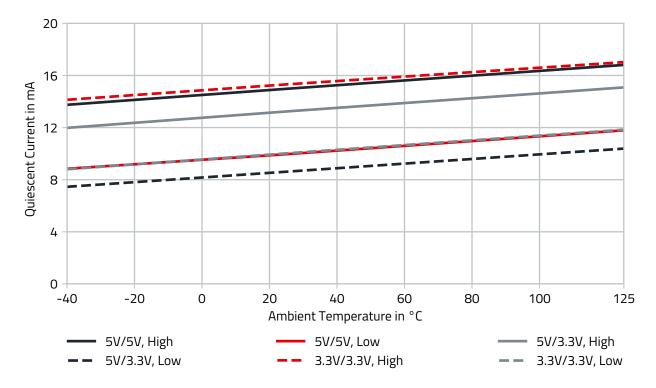

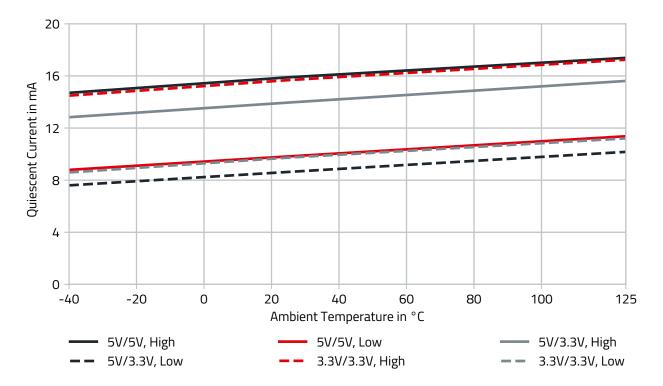

- **(8)** Supply current measurements are made with no external load connected to the integrated isolated power supply. The indicated values only describe the current required to supply the internal circuitry and external capacitive loads on the channel outputs based on the signal described in the test conditions.

Data Sheet Version 1.1 © November 2023

#### 13 ISOLATION VOLTAGE

#### 13.1 Isolation Voltage Testing

To verify the integrity of the isolation, a test voltage is applied for a specified time across a component that is designed to provide electrical isolation. This test is known as 'High Pot Test', 'Flash Tested', 'Withstand Voltage', 'Proof Voltage', 'Dielectric Withstand Voltage' or 'Isolation Test Voltage'.

All digital isolators are 100% production tested at their stated isolation voltage. This is 6 kV<sub>RMS</sub> for 1 seconds<sup>(6)</sup>.

The isolation test voltage indicated in this datasheet is for voltage transient immunity only. It does not allow this part to be used within a safety isolation system.

The digital isolator will function properly with several hundreds of volts applied continuously across the isolation barrier, however surrounding components must be individually analyzed to ensure proper insulation. Isolation measures must be taken into account to prevent any user-accessible circuitry from causing harm.

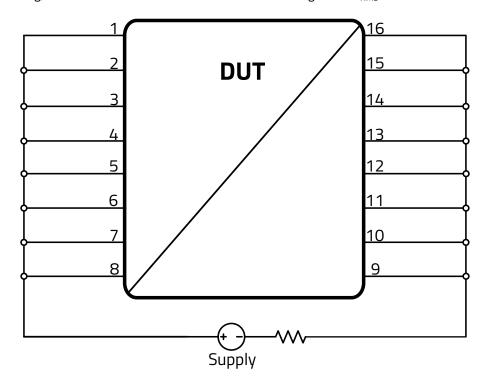

#### 13.2 Dielectric Test Setup (High Pot Test)

Connect all input terminals together then all output terminals together (see figure below) before connecting the supply voltage. When testing, set the cut-off current to 1mA with a test voltage of 6kV<sub>RMS</sub> and test time of 1s<sup>(6)</sup>.

Figure 3: Dielectric test setup.

# 13.3 Repeated High-Voltage Isolation Testing

Typically, parts can withstand multiples of their stated test voltage and still perform optimally. However, repeated exposure to high voltage test conditions will degrade the component's isolation capabilities. It is recommended to keep high voltage isolation testing to a minimum to limit degradation of the device before its installation in an application. If repeated high voltage isolation testing is required, consider reducing the voltage by a significant amount (e.g. 20%) from the stated test voltage within the datasheet.

Data Sheet Version 1.1 © November 2023

### 14 TYPICAL PERFORMANCE CURVES

If not otherwise specified, the following conditions apply:  $T_A = 25$  °C.

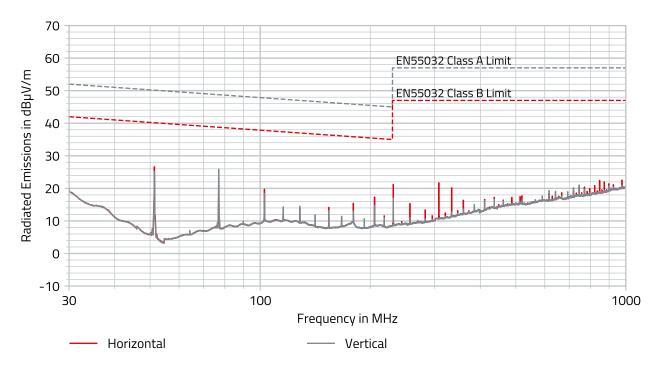

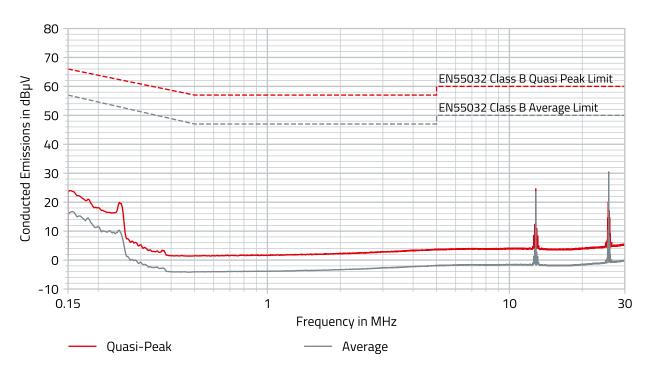

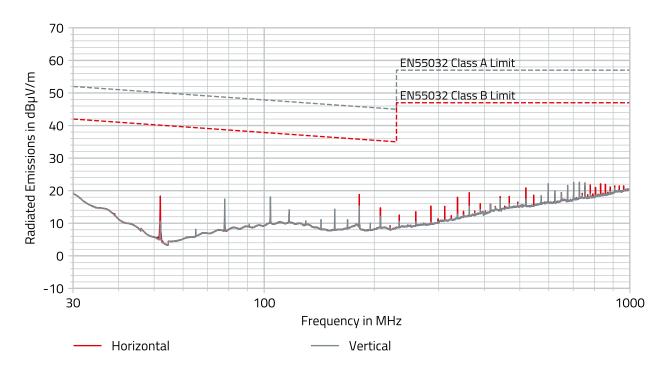

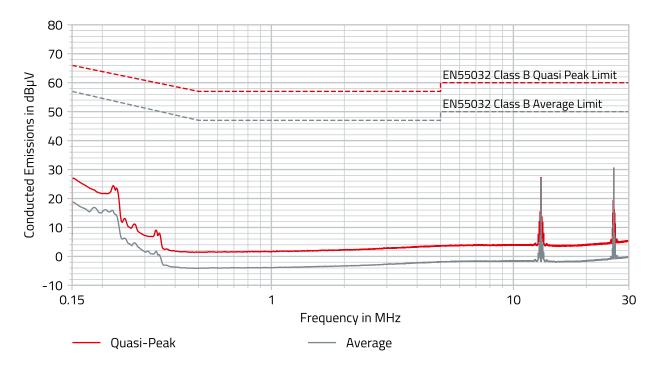

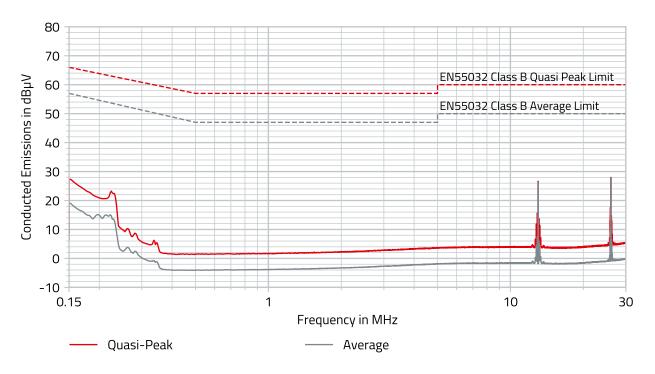

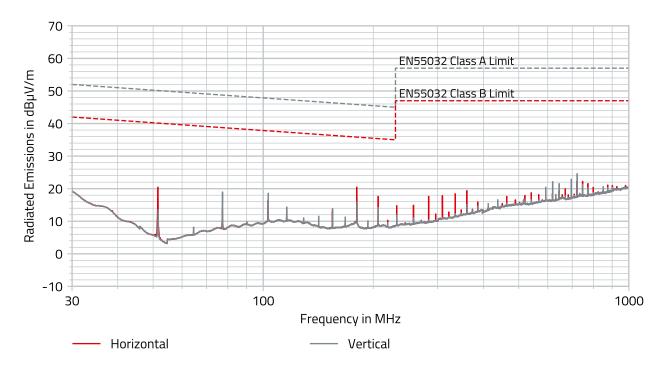

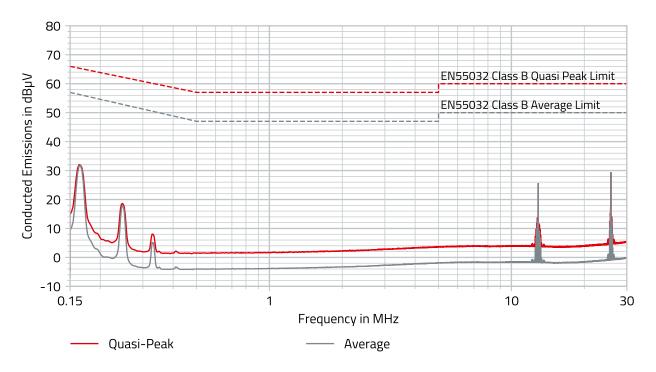

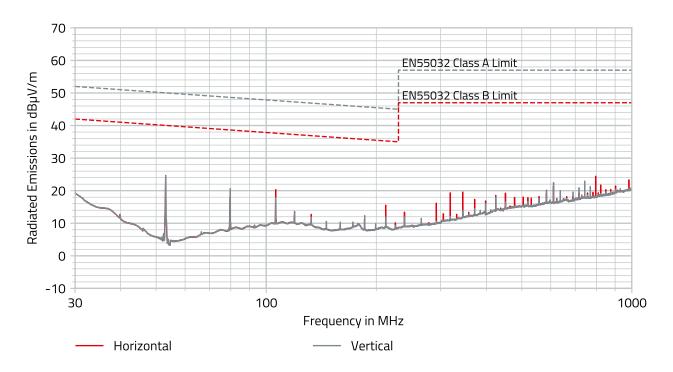

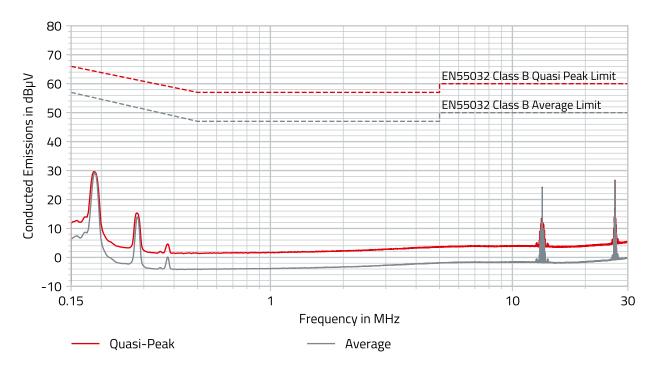

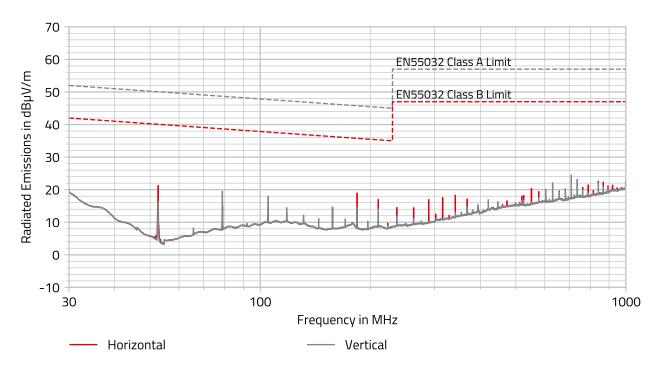

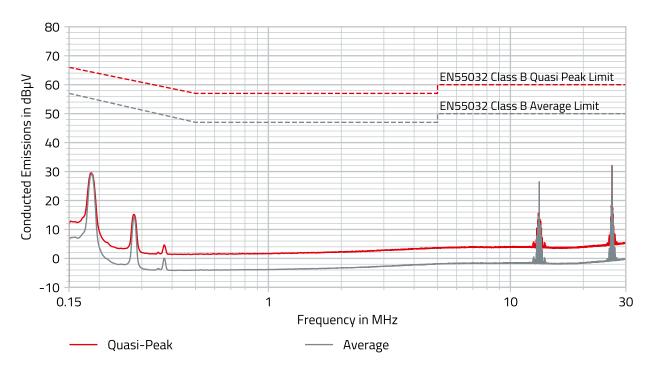

### 14.1 Radiated and Conducted Emissions (With EMI Input Filter)

The 18024x15401x digital isolators were tested in several EMC configurations to give more realistic information about implementation in the applications. The test setup is based on CISPR16 with the limit values of CISPR32. All measurements were performed with the layout and components shown in DESIGN EXAMPLE

### 14.1.1 Radiated Emissions EN55032 (CISPR-32) Class B Complaint Test Setup

- Measured in a Fully Anechoic Room (FAR) at 3m antenna distance.

- Input wire length: 160cm (80cm horizontal + 80cm vertical)

- Load directly on board

## 14.1.2 Conducted Emissions EN55032 (CISPR-32) Class B Complaint Test Setup

- Measurement input wire length: 80cm

- Load directly on board

### 14.1.3 Radiated and Conducted Emissions - 18024x15401x

Figure 4: 18024015401H radiated EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 5: 18024015401H conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 6: 18024015401L radiated EMI  $V_{CC} = 5V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0.13$ , with input filter.

Figure 7: 18024015401L conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 8: 18024115401H radiated EMI  $V_{CC} = 5V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0.13$ , with input filter.

Figure 9: 18024115401H conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 10: 18024115401L radiated EMI  $V_{CC} = 5V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0.13$ , with input filter.

Figure 11: 18024115401L conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 12: 18024215401H radiated EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 13: 18024215401H conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 14: 18024215401L radiated EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

Figure 15: 18024215401L conducted EMI  $V_{CC}$  = 5V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 0.13, with input filter.

### 14.2 DC Performance Curves

### 14.2.1 Efficiency

Figure 16: 18024x15401x efficiency.

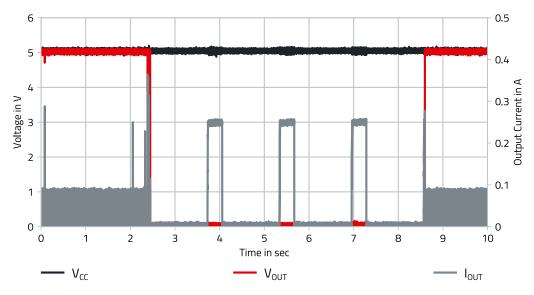

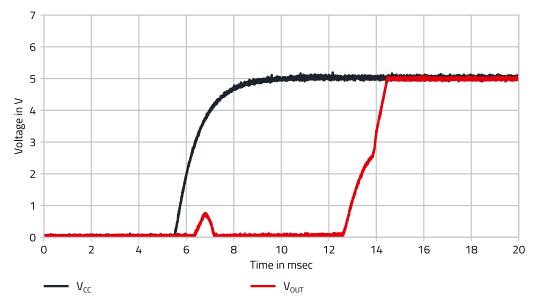

# 14.2.2 Load Transients

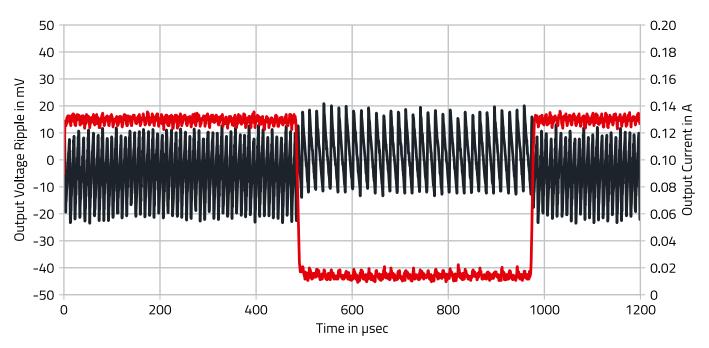

Figure 17: 18024x15401x load transient  $V_{CC} = 5V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 13$ mA to 130mA.

Figure 18: 18024x15401x load transient  $V_{CC}$  = 5V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 13mA to 130mA.

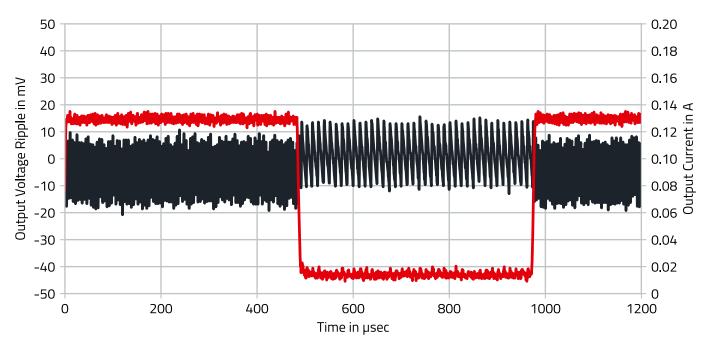

Figure 19: 18024x15401x load transient  $V_{CC} = 3.3V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 7.5$ mA to 75mA.

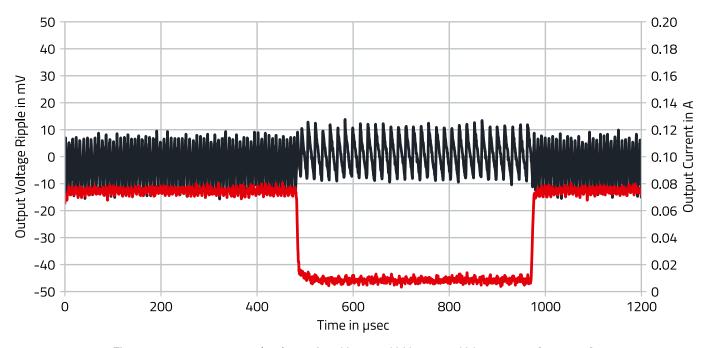

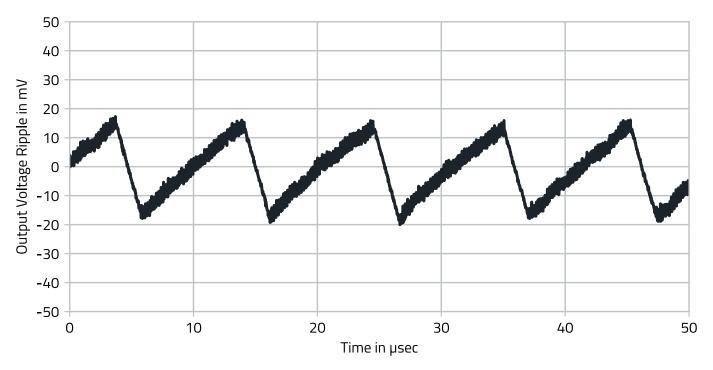

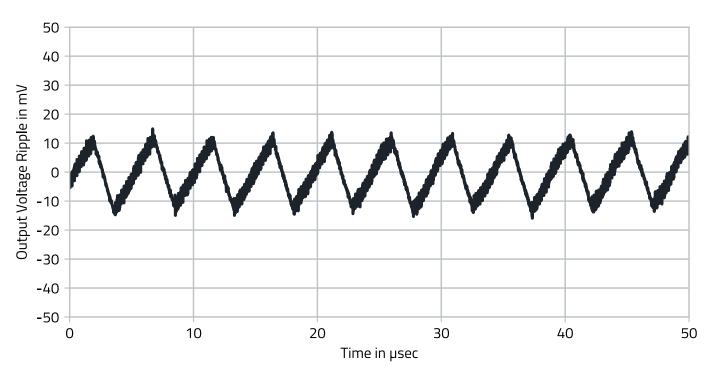

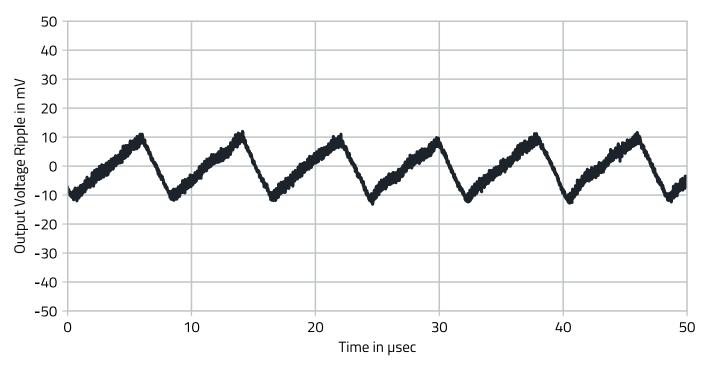

# 14.2.3 Output Voltage Ripple

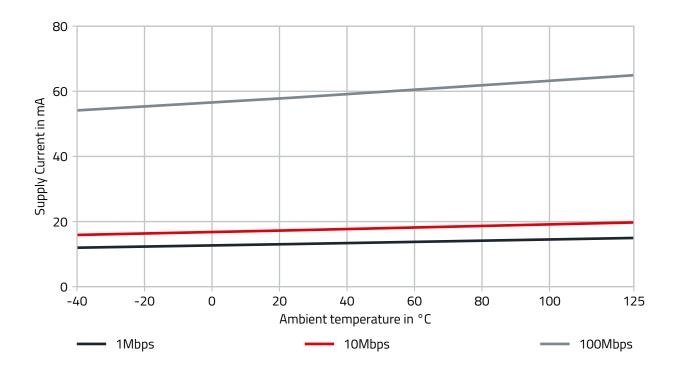

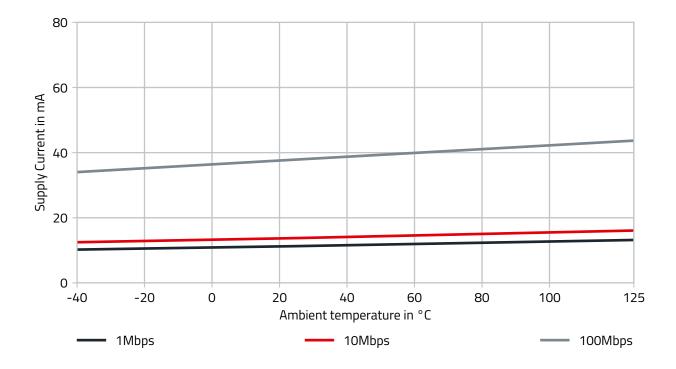

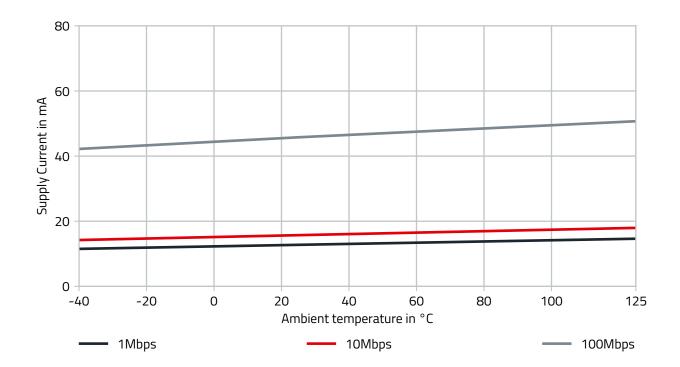

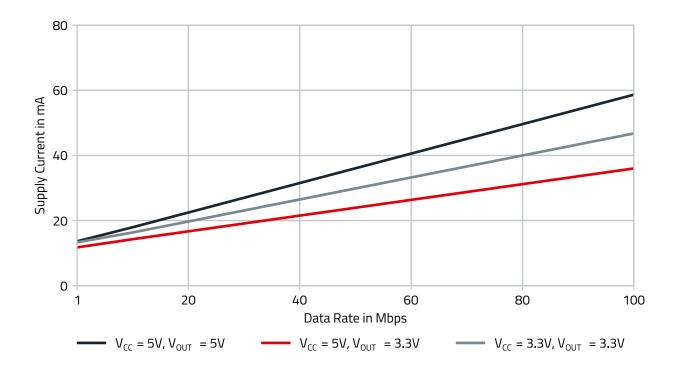

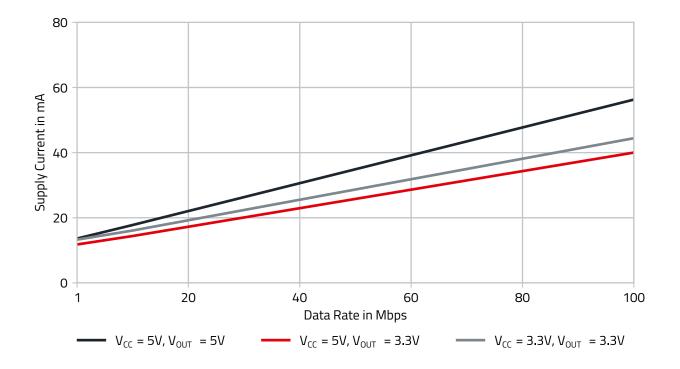

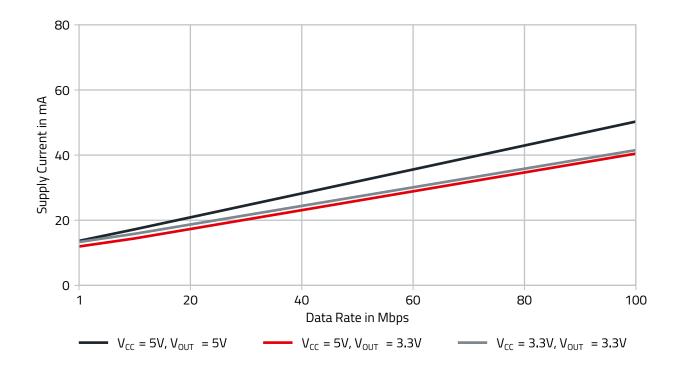

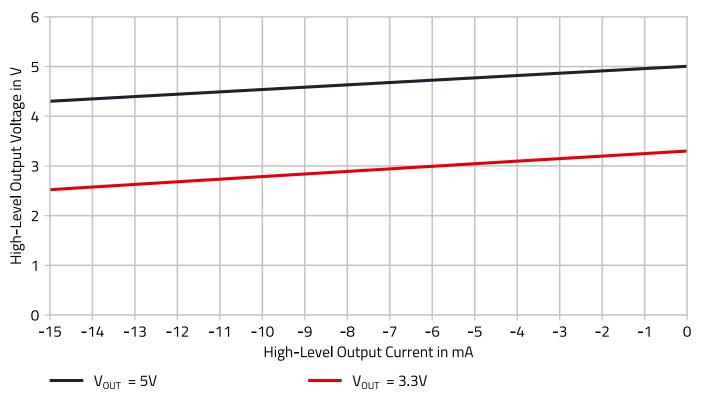

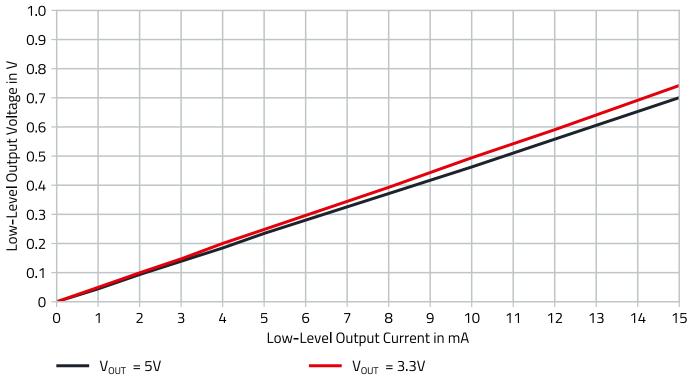

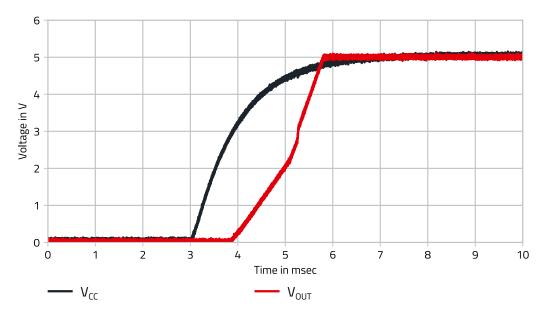

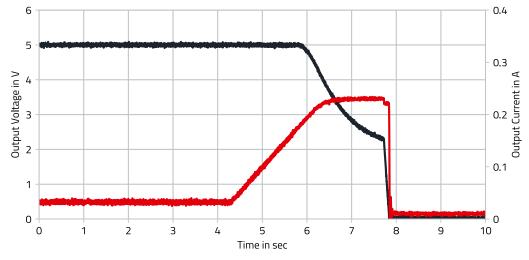

Figure 20: 18024x15401x output voltage ripple  $V_{CC} = 5V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 130$ mA.