**Bidirectional Synchronous** 100V Buck/Boost Controller with Reverse Supply, Reverse Current and Fault Protection

DESCRIPTION

#### **FEATURES**

- Bidirectional Voltage or Current Regulation

- Bidirectional Reverse Current Protection

- Input and Output Negative Voltage Protection to –40V

- Bidirectional Inrush Current Limit and Boost Output **Short Protection**

- Switching MOSFET Short Detection and Protection

- 10V Gate Drive

- Wide Input and Output Voltage Range Up to 100V

- Feedback Voltage Tolerance: ±1.0% Over Temperature

- Bidirectional Programmable Current Regulation and Monitoring

- Extensive Self-Test, Diagnostics and Fault Reporting

- Programmable Fixed or Synchronizable Switching Frequency: 80kHz to 600kHz

- Programmable Soft-Start and Dynamic Current Limit

- Masterless, Fault Tolerant Current Sharing

### **APPLICATIONS**

- Dual Battery Automotive and Industrial Systems

- High Power System Backup and Supply Stabilization

- "N+1" Redundant, High Reliability Power Supplies

- Power Interrupt Protection System

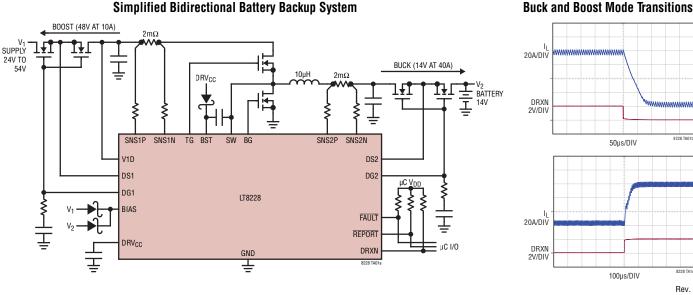

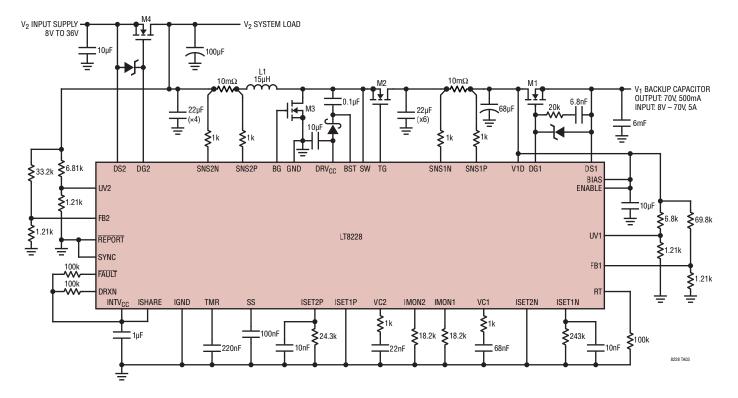

The LT<sup>®</sup>8228 is a 100V bidirectional constant-current or constant-voltage synchronous buck or boost controller with independent compensation network. The direction of the power flow is automatically determined by the LT8228 or externally controlled. The input and output protection MOSFETs protect against negative voltages, control inrush currents and provide isolation between terminals under fault conditions such as switching MOSFET shorts. In buck mode, the protection MOSFETs at the V1 terminal prevents reverse current. In boost mode, the same MOSFETs regulate the output inrush current and protects itself with an adjustable timer circuit breaker.

The LT8228 offers bidirectional input and output current limit as well as independent current monitoring. Masterless, fault tolerant current sharing allows any LT8228 in parallel to be added or subtracted while maintaining current sharing accuracy. Internal and external fault diagnostics and reporting are available via the FAULT and REPORT pins. The LT8228 is available in a 38-lead TSSOP package.

All registered trademarks and trademarks are the property of their respective owners

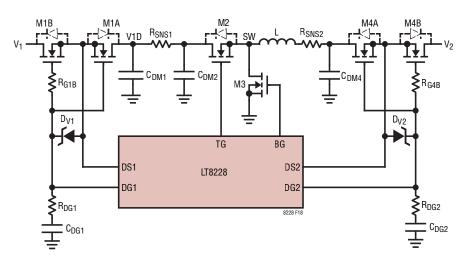

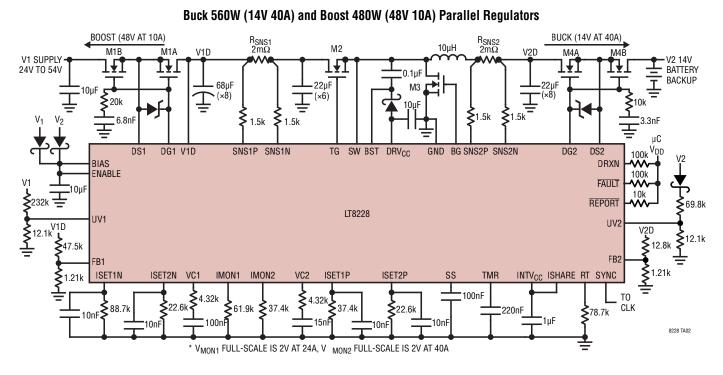

## TYPICAL APPLICATION

Rev. A

## TABLE OF CONTENTS

| Features                                                           | 1    |

|--------------------------------------------------------------------|------|

| Applications                                                       | 1    |

| Typical Application                                                | 1    |

| Description                                                        |      |

| Absolute Maximum Ratings                                           | 3    |

| Order Information                                                  | 3    |

| Pin Configuration                                                  | 3    |

| Electrical Characteristics                                         |      |

| Typical Performance Characteristics                                | 9    |

| Buck Efficiency and Operation                                      |      |

| Typical Performance Characteristics                                |      |

| Boost Efficiency and Operation                                     |      |

| ENABLE, Supply Current and V <sub>CC</sub>                         | 13   |

| SS Current, Frequency, Thresholds and Driver                       | 15   |

| Protection MOSFET Controller                                       |      |

| Pin Functions                                                      |      |

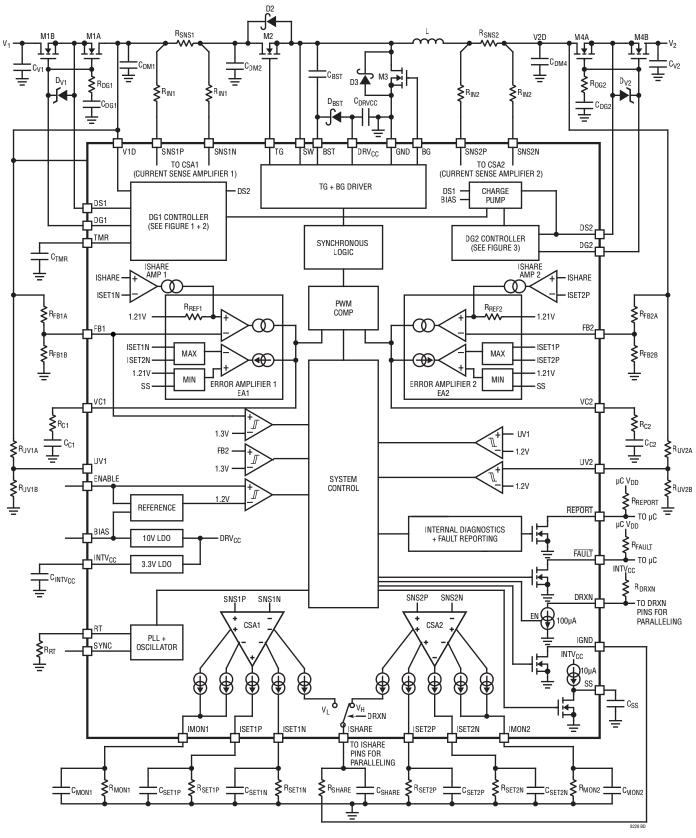

| Block Diagram                                                      |      |

| Operation                                                          |      |

| Overview                                                           | 24   |

| Buck Mode Operation                                                | 24   |

| Boost Mode Operation                                               | 25   |

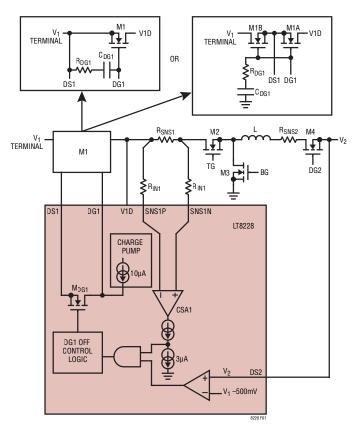

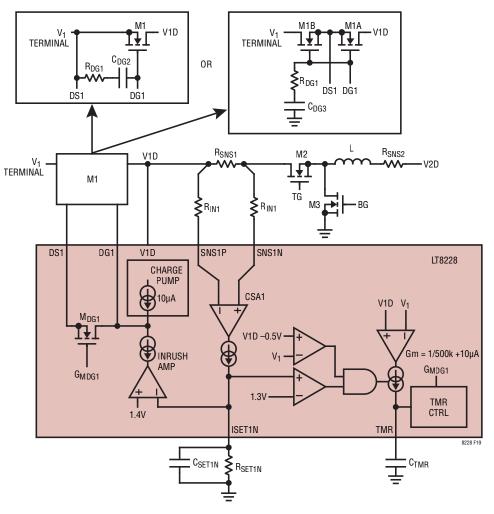

| V <sub>1</sub> Protection MOSFET Controller Operation              | 26   |

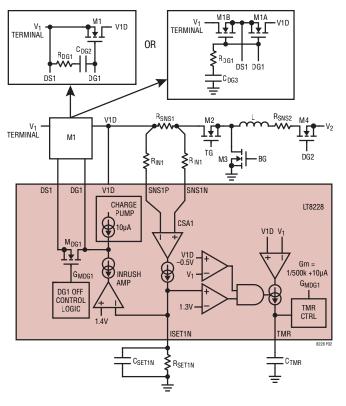

| V <sub>2</sub> Protection MOSFET Controller Operation              | 28   |

| Mode of Operation (DRXN)                                           | 28   |

| Enable and Soft-Start (Enable and SS)                              |      |

| Paralleling Multiple Controllers (ISHARE                           |      |

| and IGND)                                                          | 30   |

| BIAS Supply and V <sub>CC</sub> Regulators                         | 31   |

| Strong Gate Drivers                                                | 32   |

| Frequency Selection, Spread Spectrum and Phase                     | -    |

| Locked Loop (RT and SYNC)                                          |      |

| FAULT Monitoring and REPORT Feature                                | 32   |

| Applications Information                                           | . 33 |

| Introduction                                                       |      |

| Programming the Switching Frequency                                | 33   |

| Inductor Selection                                                 | 34   |

| R <sub>SNS2</sub> and R <sub>IN2</sub> Selection for Peak Inductor |      |

| Current                                                            | 35   |

|                                                                    |      |

| R <sub>SET2P</sub> Selection for V <sub>2</sub> Output Current<br>Limit (Buck Mode) | 26 |

|-------------------------------------------------------------------------------------|----|

| $R_{SET2N}$ Selection for V <sub>2</sub> Input Current                              | 30 |

| Limit (Boost Mode)                                                                  | 37 |

| $R_{MON2}$ Selection for V <sub>2</sub> Current Monitoring                          |    |

| $R_{SNS1}$ and $R_{IN1}$ Selection                                                  |    |

| $R_{SET1P}$ Selection for V <sub>1</sub> Input Current                              |    |

| Limit (Buck Mode)                                                                   | 39 |

| $R_{SFT1N}$ Selection for V <sub>1</sub> Output Current                             |    |

| Limit (Boost Mode)                                                                  | 40 |

| R <sub>MON1</sub> Selection for V <sub>1</sub> Current Monitoring                   | 41 |

| Output Voltage, Input Undervoltage and Output                                       |    |

| Overvoltage Programming                                                             | 41 |

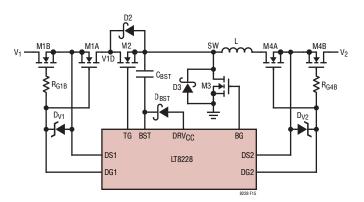

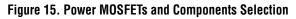

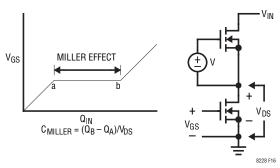

| Power MOSFET Selection and Efficiency                                               |    |

| Considerations                                                                      | 42 |

| Optional Schottky Diode (D2 and D3) Selection                                       | 45 |

| Top MOSFET Driver Supply (C <sub>BST</sub> , D <sub>BST</sub> )                     |    |

| Power Path Capacitor Selection                                                      | 46 |

| Loop Compensation                                                                   |    |

| Inrush Current Control                                                              |    |

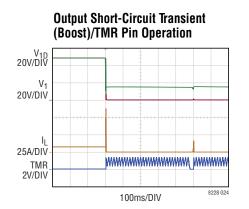

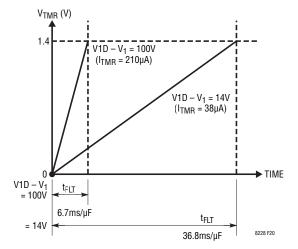

| Boost Output Short Protection and Timer                                             | 50 |

| FAULT Conditions                                                                    | 52 |

| <u>Soft-Sta</u> rt                                                                  |    |

| REPORT Feature                                                                      |    |

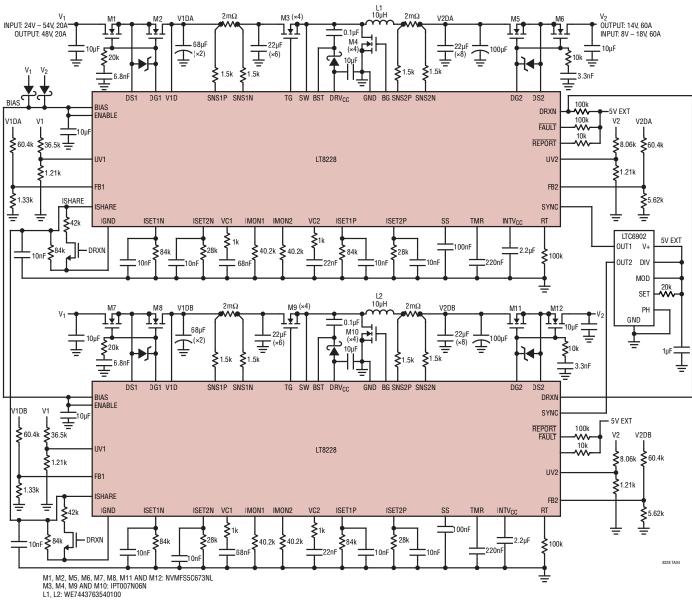

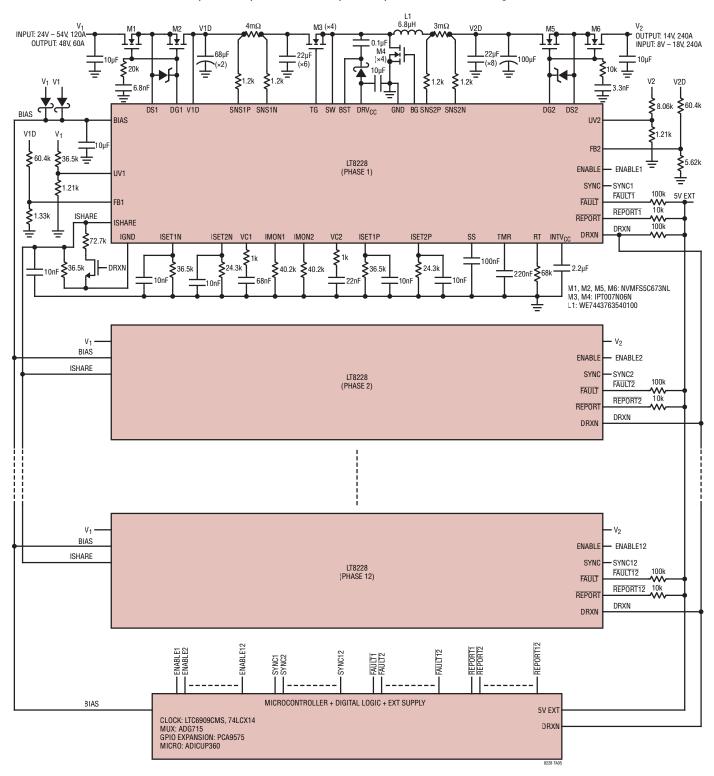

| Paralleling Multiple LT8228s                                                        |    |

| BIAS, $DRV_{CC}$ , $INTV_{CC}$ and Power Dissipation                                |    |

| Thermal Shutdown                                                                    |    |

| Pin Clearance/Creepage Consideration                                                |    |

| Efficiency Considerations                                                           |    |

| PC Board Layout Checklist                                                           |    |

| Design Example                                                                      |    |

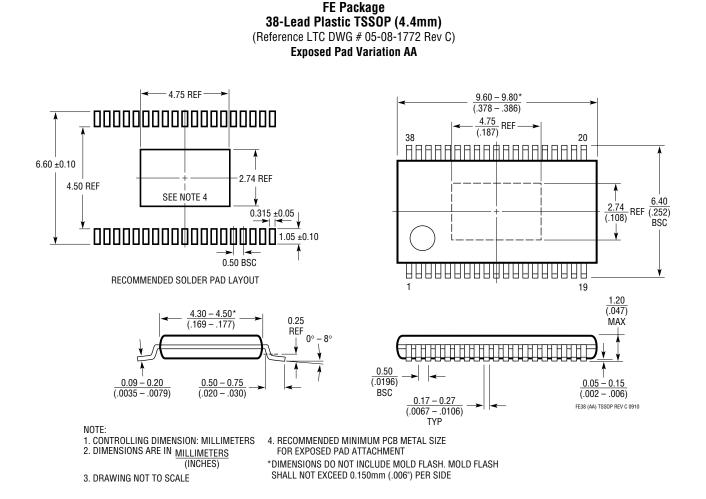

| Package Description                                                                 |    |

| Revision History                                                                    |    |

| Typical Application                                                                 |    |

| Related Parts                                                                       | 09 |

#### **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1 | ) |

|-------|---|---|

|-------|---|---|

| DS1, DS240V to 100V                               |

|---------------------------------------------------|

| DG1 (Note 2) DS1 –0.3V to DS1 + 15V               |

|                                                   |

| DG2 (Note 3) DS2 -0.3V to DS2 + 15V               |

| ENABLE, V1D, BIAS100V                             |

| SNS1P, SNS2P, SNS1N, SNS2N 100V                   |

| SNS1P - SNS1N, SNS2P - SNS2N±0.3V                 |

| SW (Note 4)                                       |

| DRV <sub>CC</sub> (Note 5), BST – SW15V           |

| TG, BG (Note 6)                                   |

| INTV <sub>CC</sub> (Note 7)4V                     |

|                                                   |

| ISET1P, ISET1N, ISHARE INTV <sub>CC</sub>         |

| ISET2P, ISET2N INTV <sub>CC</sub>                 |

| VC1, VC2, RT, SS, IMON1, IMON2 INTV <sub>CC</sub> |

| FB1, UV1, FB2, UV25.5V                            |

| DRXN, SYNC, IGND, FAULT, REPORT                   |

| Operating Junction Temperature Range              |

| LT8228E, I (Notes 8, 9)40°C to 125°C              |

|                                                   |

| LT8228H (Notes 8, 9)40°C to 150°C                 |

| Storage Temperature Range –65°C to 175°C          |

|                                                   |

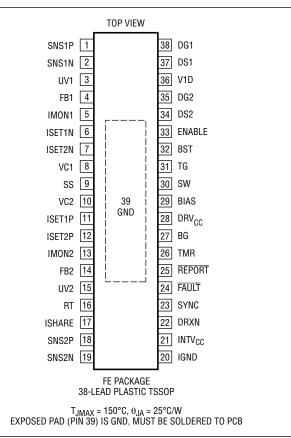

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|-----------------|---------------|-----------------------|-------------------|

| LT8228EFE#PBF    | LT8228EFE#TRPBF | LT8228FE      | 38-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8228IFE#PBF    | LT8228IFE#TRPBF | LT8228FE      | 38-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8228HFE#PBF    | LT8228HFE#TRPBF | LT8228FE      | 38-Lead Plastic TSSOP | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

Rev. A

| SYMBOL                                 | PARAMETER                                                                                         | CONDITIONS                                                           |   | MIN          | ТҮР          | MAX          | UNITS    |

|----------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---|--------------|--------------|--------------|----------|

| V <sub>1</sub>                         | Buck Mode Input Voltage                                                                           |                                                                      | • | 6            |              | 100          | V        |

| V <sub>2</sub>                         | Boost Mode Input Voltage                                                                          |                                                                      | • | 6            |              | 100          | V        |

| V <sub>BIAS</sub>                      | BIAS Operating Voltage Range                                                                      |                                                                      | • | 8            |              | 100          | V        |

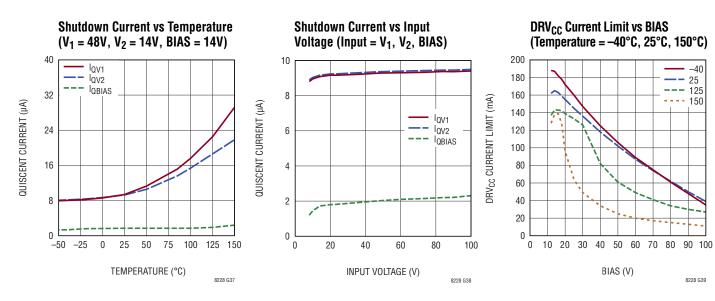

| I <sub>QV1</sub>                       | DS1 Quiescent Current (Shutdown)<br>DS1 Quiescent Current (Not Switching)                         | ENABLE = $0V$<br>ENABLE = $2V$ , $V_{UV1} = V_{UV2} = 0V$            | • |              | 10<br>200    | 45<br>350    | μA<br>μA |

| I <sub>QV2</sub>                       | DS2 Quiescent Current (Shutdown)<br>DS2 Quiescent Current (Not Switching)                         | ENABLE = $0V$<br>ENABLE = $2V$ , $V_{UV1} = V_{UV2} = 0V$            | • |              | 10<br>10     | 40<br>20     | μA<br>μA |

| I <sub>QBIAS</sub>                     | BIAS Quiescent Current (Shutdown)<br>BIAS Quiescent Current (Not Switching)                       | ENABLE = 0V<br>ENABLE = 2V, V <sub>UV1</sub> = V <sub>UV2</sub> = 0V | • |              | 4<br>3.7     | 10<br>5      | μA<br>mA |

| I <sub>SS</sub>                        | Soft-Start Current (Note 10)                                                                      | SS = 0V                                                              | • | 9.5          | 10           | 10.5         | μA       |

| Threshold Volta                        | ges                                                                                               |                                                                      |   |              |              |              |          |

| EN <sub>THRESH</sub>                   | ENABLE Threshold (Falling)<br>ENABLE Hysteresis                                                   |                                                                      | • | 1.16         | 1.20<br>100  | 1.24         | V<br>mV  |

| UV <sub>V1</sub>                       | UV1 Voltage Threshold (Falling)<br>UV1 Hysteresis                                                 |                                                                      | • | 1.18         | 1.20<br>100  | 1.22         | V<br>mV  |

| UV <sub>V2</sub>                       | UV2 Voltage Threshold (Falling)<br>UV2 Hysteresis                                                 |                                                                      | • | 1.18         | 1.20<br>100  | 1.22         | V<br>mV  |

| 0V <sub>V1</sub>                       | FB1 Over Voltage Threshold (Rising)<br>FB1 Over Voltage Hysteresis                                |                                                                      | • | 1.28         | 1.30<br>100  | 1.32         | V<br>mV  |

| 0V <sub>V2</sub>                       | FB2 Over Voltage Threshold (Rising)<br>FB2 Over Voltage Hysteresis                                |                                                                      | • | 1.28         | 1.30<br>100  | 1.32         | V<br>mV  |

| DRXN                                   | DRXN Logic Threshold (Rising)<br>DRXN Logic Threshold (Falling)                                   |                                                                      | • | 1.05<br>0.75 | 1.10<br>0.80 | 1.15<br>0.85 | V<br>V   |

| SYNC                                   | SYNC Logic Threshold (Rising)<br>SYNC Logic Threshold (Falling)                                   |                                                                      | • | 0.65         | 0.95<br>0.80 | 1.10         | V<br>V   |

| ISHARETHRESH                           | ISHARE Disable Threshold (Rising)<br>ISHARE Disable Hysteresis                                    |                                                                      | • | 2.45         | 2.49<br>0.40 | 2.53         | V<br>V   |

| V <sub>CC</sub> Regulator              | ·                                                                                                 |                                                                      |   |              |              |              |          |

| V <sub>DRVCC</sub>                     | DRV <sub>CC</sub> Regulation Voltage                                                              | 12V < V <sub>BIAS</sub> < 100V                                       | • | 9.7          | 10           | 10.5         | V        |

| $\Delta V_{DRVCC}$                     | DRV <sub>CC</sub> Load Regulation                                                                 | I <sub>DRVCC</sub> = 0mA to 100mA                                    |   |              | 1.0          | 2.5          | %        |

| IDRVCCMAX                              | DRV <sub>CC</sub> Current Limit (Note 10)                                                         | $V_{BIAS} = 14V, V_{DRVCC} = 8V$                                     | • | 100          | 160          |              | mA       |

| DRV <sub>CCUV</sub>                    | DRV <sub>CC</sub> Undervoltage Threshold (Falling)<br>DRV <sub>CC</sub> Undervoltage Hysteresis   |                                                                      | • | 6.1          | 6.35<br>300  | 6.6          | V<br>mV  |

| DRV <sub>CCOV</sub>                    | DRV <sub>CC</sub> Overvoltage Threshold (Rising)<br>DRV <sub>CC</sub> Overvoltage Hysteresis      |                                                                      | • | 14.6         | 15.1<br>1.0  | 15.6         | V<br>V   |

| V <sub>BIAS</sub> – V <sub>DRVCC</sub> | DRV <sub>CC</sub> Dropout Voltage                                                                 | V <sub>BIAS</sub> = 10V, I <sub>DRVCC</sub> = 100mA                  | • |              | 1.0          | 3.5          | V        |

| VINTVCC                                | INTV <sub>CC</sub> Regulation Voltage                                                             |                                                                      | • | 3.8          | 4.0          | 4.3          | V        |

| INTV <sub>CCUV</sub>                   | INTV <sub>CC</sub> Undervoltage Threshold (Falling)<br>INTV <sub>CC</sub> Undervoltage Hysteresis |                                                                      | • | 3.45         | 3.6<br>0.2   | 3.75         | V<br>V   |

| INTV <sub>CCOV</sub>                   | INTV <sub>CC</sub> Overvoltage Threshold (Rising)<br>INTV <sub>CC</sub> Overvoltage Hysteresis    |                                                                      | • | 4.50         | 4.7<br>0.5   | 4.85         | V<br>V   |

| SYMBOL                                                           | PARAMETER                                                                    | CONDITIONS                                                                                                                                                                                    |                       | MIN                                                 | ТҮР                                                      | MAX                                                        | UNITS                                  |

|------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------|----------------------------------------|

| Protection MOS                                                   | FET at V <sub>1</sub> Terminal Controller                                    |                                                                                                                                                                                               |                       |                                                     |                                                          |                                                            |                                        |

| $\Delta V_{DG1}$                                                 | DG1 Gate Drive<br>(DG1 – DS1)                                                | $V_{DS1} = 6V, V_{DS2} = 0V, BIAS = 8V$<br>$V_{DS1} = 0V, V_{DS2} = 0V, BIAS = 8V$                                                                                                            | •                     | 8.0<br>8.0<br>8.0                                   | 10                                                       | 12.5                                                       | V<br>V<br>V                            |

| I <sub>DG1UP</sub>                                               | DG1 Pull-Up Current (Note 10)                                                | $V_{DG1} = V_{DS1} = 48V, V_{DG2} = V_{DS2} = 14V$                                                                                                                                            |                       | 7                                                   | 10                                                       | 13                                                         | μA                                     |

| I <sub>DG1DOWN</sub>                                             | DG1 Pull-Down Current (Note 10)                                              | $V_{DG1} - V_{DS1} = 5V$                                                                                                                                                                      |                       | -110                                                | -80                                                      | -60                                                        | mA                                     |

| V <sub>1NEGATIVE</sub>                                           | Negative DS1 Voltage Threshold for DG1 Off                                   | $V_{DG1} = 0V, I_{DG1} = -1mA$                                                                                                                                                                |                       | -2.2                                                | -1.7                                                     |                                                            | V                                      |

| IREVERSEV1                                                       | DS1 Reverse Leakage Current                                                  | $V_{DS1} = -35V$                                                                                                                                                                              |                       |                                                     |                                                          | 0.6                                                        | mA                                     |

| V <sub>SET1NMAX</sub>                                            | ISET1N Boost Output Inrush limit in Boost<br>Mode (Note 11)                  | $V_{DS1} = 8V, V_{DG1} - V_{DS1} = 2.5V, I_{DG1} = 0, DRXN = 0V, SS > 1.5V (Boost)$                                                                                                           | •                     | 1.35                                                | 1.40                                                     | 1.45                                                       | V                                      |

| V <sub>SNS1P,1N</sub> (RCUR)                                     | Buck Mode Reverse Current Threshold for DG1 Off (V <sub>SNS1P,SNSN1N</sub> ) | $V_{DS2} = 14V, DRXN = 2V (Buck)$                                                                                                                                                             | •                     | -5.0                                                | -3.0                                                     | -1.0                                                       | mV                                     |

| V <sub>DG1UV</sub>                                               | DG1 Undervoltage Threshold (Falling)<br>DG1 Undervoltage Hysteresis          |                                                                                                                                                                                               | •                     | 3.8                                                 | 4.5<br>0.5                                               | 5.0                                                        | V<br>V                                 |

| Protection MOS                                                   | FET at V <sub>2</sub> Terminal Controller                                    |                                                                                                                                                                                               |                       |                                                     |                                                          |                                                            |                                        |

| $\Delta V_{DG2}$                                                 | DG2 Gate Drive<br>(DG2 – DS2)                                                | $V_{DS1} = 0V, V_{DS2} = 6V, BIAS = 8V$<br>$V_{DS1} = 0V, V_{DS2} = 0V, BIAS = 8V$                                                                                                            | •                     | 8.0<br>8.0<br>8.0                                   | 10                                                       | 12.5                                                       | V<br>V<br>V                            |

| I <sub>DG2UP</sub>                                               | DG2 Pull-Up Current (Note 10)                                                | $V_{DG1} = V_{DS1} = 48V, V_{DG2} = V_{DS2} = 14V$                                                                                                                                            |                       | 7                                                   | 10                                                       | 13                                                         | μA                                     |

| I <sub>DG2DOWN</sub>                                             | DG2 Pull-Down Current (Note 10)                                              | $V_{DG2} - V_{DS2} = 5V$                                                                                                                                                                      |                       | -110                                                | -80                                                      | -60                                                        | mA                                     |

| V <sub>2NEGATIVE</sub>                                           | Negative DS2 Voltage Threshold for DG2 Off                                   | $V_{DG2} = 0V$ , $I_{DG2} = -1mA$                                                                                                                                                             |                       | -2.2                                                | -1.7                                                     |                                                            | V                                      |

| I <sub>REVERSEV2</sub>                                           | DS2 Reverse Leakage Current                                                  | $V_{DS2} = -35V$                                                                                                                                                                              |                       |                                                     |                                                          | 0.6                                                        | mA                                     |

| V <sub>DG2UV</sub>                                               | DG2 Undervoltage Threshold (Falling)<br>DG2 Undervoltage Hysteresis          |                                                                                                                                                                                               | •                     | 3.8                                                 | 4.4<br>0.5                                               | 5.0                                                        | V<br>V                                 |

| Current Sense A                                                  | Amplifiers (Note 12)                                                         |                                                                                                                                                                                               |                       |                                                     |                                                          |                                                            |                                        |

| I <sub>B1</sub>                                                  | SNS1P, SNS1N Bias Current                                                    | 2.5V < V <sub>CM1</sub> < 100V<br>V <sub>CM1</sub> = 0V                                                                                                                                       | •                     | -105<br>35                                          | -90<br>50                                                | -70<br>70                                                  | μA<br>μA                               |

| I <sub>ISET1P</sub>                                              | ISET1P Output Current<br>2.5V < V <sub>CM1</sub> < 100V                      | V <sub>RSNS1</sub> = 1mV<br>V <sub>RSNS1</sub> = 25mV<br>V <sub>RSNS1</sub> = 50mV<br>V <sub>RSNS1</sub> = 80mV                                                                               | ••••                  | 0.0<br>24.0<br>48.5<br>78.0                         | 1.0<br>25.0<br>50.0<br>80.0                              | 2.2<br>26.0<br>51.5<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

| I <sub>ISET1N</sub>                                              | ISET1N Output Current<br>2.5V < V <sub>CM1</sub> < 100V                      | $ \begin{array}{l} V_{RSNS1} = -1mV \\ V_{RSNS1} = -25mV \\ V_{RSNS1} = -50mV \\ V_{RSNS1} = -80mV \end{array} $                                                                              | •                     | 0.0<br>24.0<br>48.5<br>78.0                         | 1.0<br>25.0<br>50.0<br>80.0                              | 2.2<br>26.0<br>51.5<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

| I <sub>IMON1</sub>                                               | IMON1 Output Current<br>2.5V < V <sub>CM1</sub> < 100V                       | $\begin{array}{l} V_{RSNS1} = -80mV \\ V_{RSNS1} = -50mV \\ V_{RSNS1} = -25mV \\ V_{RSNS1} = -1mV \\ V_{RSNS1} = 1mV \\ V_{RSNS1} = 25mV \\ V_{RSNS1} = 50mV \\ V_{RSNS1} = 80mV \end{array}$ | •<br>•<br>•<br>•<br>• | 78.0<br>48.5<br>24.0<br>0.0<br>24.0<br>48.5<br>78.0 | 80<br>50.0<br>25.0<br>1.0<br>1.0<br>25.0<br>50.0<br>80.0 | 82.0<br>51.5<br>26.0<br>2.2<br>2.2<br>26.0<br>51.5<br>82.0 | Αμ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

| I <sub>ISET1P</sub> , I <sub>ISET1N</sub> ,<br>I <sub>MON1</sub> | Output Current, V <sub>CM1</sub> < 2.5V                                      | V <sub>RSNS1</sub>   = 1mV<br> V <sub>RSNS1</sub>   = 25mV<br> V <sub>RSNS1</sub>   = 50mV<br> V <sub>RSNS1</sub>   = 80mV                                                                    | •                     | 0.0<br>22.5<br>47.5<br>76.0                         | 1.0<br>25.0<br>50.0<br>80.0                              | 3.0<br>27.5<br>52.5<br>84.0                                | μΑ<br>μΑ<br>μΑ<br>μΑ                   |

| SYMBOL                                                             | PARAMETER                                                                                       | CONDITIONS                                                                                                                                                                                                                             |             | MIN                                                        | ТҮР                                                        | MAX                                                        | UNITS                                  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|

| I <sub>B2</sub>                                                    | SNS2P, SNS2N Bias Current                                                                       | 2.5V < V <sub>CM2</sub> < 100V<br>V <sub>CM2</sub> = 0V                                                                                                                                                                                | •           | -105<br>35                                                 | -90<br>50                                                  | -70<br>70                                                  | μA<br>μA                               |

| I <sub>ISET2P</sub>                                                | ISET2P Output Current<br>2.5V < V <sub>CM2</sub> < 100V                                         | V <sub>RSNS2</sub> = 1mV<br>V <sub>RSNS2</sub> = 25mV<br>V <sub>RSNS2</sub> = 50mV<br>V <sub>RSNS2</sub> = 80mV                                                                                                                        | •<br>•<br>• | 0.0<br>24.0<br>48.5<br>78.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 2.2<br>26.0<br>51.5<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

| I <sub>ISET2N</sub>                                                | ISET2N Output Current<br>2.5V < V <sub>CM2</sub> < 100V                                         | $V_{RSNS2} = -1mV$ $V_{RSNS2} = -25mV$ $V_{RSNS2} = -50mV$ $V_{RSNS2} = -80mV$                                                                                                                                                         | •<br>•<br>• | 0.0<br>24.0<br>48.5<br>78.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 2.2<br>26.0<br>51.5<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

| I <sub>IMON2</sub>                                                 | IMON2 Output Current<br>2.5V < V <sub>CM2</sub> < 100V                                          | V <sub>RSNS2</sub> = -80mV<br>V <sub>RSNS2</sub> = -50mV<br>V <sub>RSNS2</sub> = -25mV<br>V <sub>RSNS2</sub> = -1mV<br>V <sub>RSNS2</sub> = 1mV<br>V <sub>RSNS2</sub> = 25mV<br>V <sub>RSNS2</sub> = 50mV<br>V <sub>RSNS2</sub> = 80mV |             | 78.0<br>48.5<br>24.0<br>0.0<br>0.0<br>24.0<br>48.5<br>78.0 | 80.0<br>50.0<br>25.0<br>1.0<br>1.0<br>25.0<br>50.0<br>80.0 | 82.0<br>51.5<br>26.0<br>2.2<br>2.2<br>26.0<br>51.5<br>82.0 | Αμ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

| I <sub>ISET2P</sub> , I <sub>ISET2N</sub> ,<br>I <sub>MON2</sub> , | Output Current, V <sub>CM1</sub> < 2.5V                                                         | $\begin{array}{l}  V_{RSNS1}  = 1mV \\  V_{RSNS1}  = 25mV \\  V_{RSNS1}  = 50mV \\  V_{RSNS1}  = 80mV \end{array}$                                                                                                                     | •           | 0.0<br>22.5<br>47.5<br>76.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 3.0<br>27.5<br>52.5<br>84.0                                | μΑ<br>μΑ<br>μΑ<br>μΑ                   |

| I <sub>ISHARE</sub>                                                | ISHARE Output Current, ISHARE = 0V<br>DRXN = 0V (Boost Mode),<br>2.5V < V <sub>CM1</sub> < 100V | $ \begin{array}{l} V_{RSNS1} = -1mV \\ V_{RSNS1} = -25mV \\ V_{RSNS1} = -50mV \\ V_{RSNS1} = -80mV \end{array} $                                                                                                                       | •<br>•<br>• | 0.0<br>24.0<br>48.5<br>78.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 2.2<br>26.0<br>51.0<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

|                                                                    | ISHARE Output Current, ISHARE = 0V<br>DRXN = 2V (Buck Mode),<br>2.5V < V <sub>CM1</sub> < 100V  | V <sub>RSNS2</sub> = 1mV<br>V <sub>RSNS2</sub> = 25mV<br>V <sub>RSNS2</sub> = 50mV<br>V <sub>RSNS2</sub> = 80mV                                                                                                                        | •           | 0.0<br>24.0<br>48.5<br>78.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 2.2<br>26.0<br>51.0<br>82.0                                | μΑ<br>μΑ<br>μΑ                         |

|                                                                    | ISHARE Output Current, ISHARE = 0V<br>DRXN = 0V (Boost Mode),<br>V <sub>CM1</sub> < 2.5V        | $ \begin{array}{l} V_{RSNS1} = -1mV \\ V_{RSNS1} = -25mV \\ V_{RSNS1} = -50mV \\ V_{RSNS1} = -80mV \end{array} $                                                                                                                       | •           | 0.0<br>22.5<br>47.5<br>76.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 3.0<br>27.5<br>52.5<br>84.0                                | μΑ<br>μΑ<br>μΑ                         |

|                                                                    | ISHARE Output Current, ISHARE = 0V<br>DRXN = 2V (Buck Mode),<br>V <sub>CM2</sub> < 2.5V         | V <sub>RSNS2</sub> = 1mV<br>V <sub>RSNS2</sub> = 25mV<br>V <sub>RSNS2</sub> = 50mV<br>V <sub>RSNS2</sub> = 80mV                                                                                                                        | •           | 0.0<br>22.5<br>47.5<br>76.0                                | 1.0<br>25.0<br>50.0<br>80.0                                | 3.0<br>27.5<br>52.5<br>84.0                                | μΑ<br>μΑ<br>μΑ                         |

| Buck Voltage a                                                     | nd Current Regulation                                                                           |                                                                                                                                                                                                                                        |             |                                                            |                                                            |                                                            |                                        |

| V <sub>FB2</sub>                                                   | FB2 Regulation Voltage (Note 13)                                                                |                                                                                                                                                                                                                                        | •           | 1.198                                                      | 1.210                                                      | 1.222                                                      | V                                      |

| I <sub>FB2</sub>                                                   | FB2 Pin Bias Current                                                                            |                                                                                                                                                                                                                                        |             |                                                            | 10                                                         | 50                                                         | nA                                     |

| g <sub>mFB1</sub>                                                  | V <sub>2</sub> Error Amplifier Transconductance                                                 |                                                                                                                                                                                                                                        |             |                                                            | 0.8                                                        |                                                            | ms                                     |

| V <sub>ISET1P</sub>                                                | ISET1P Regulation Voltage (Note 14)                                                             |                                                                                                                                                                                                                                        | •           | 1.198                                                      | 1.210                                                      | 1.222                                                      | V                                      |

| gmISET1P                                                           | ISET1P Error Amplifier Transconductance                                                         |                                                                                                                                                                                                                                        |             |                                                            | 0.8                                                        |                                                            | ms                                     |

| V <sub>ISET2P</sub>                                                | ISET2P Regulation Voltage (Note 14)                                                             |                                                                                                                                                                                                                                        | •           | 1.198                                                      | 1.210                                                      | 1.222                                                      | V                                      |

| g <sub>mISET2P</sub>                                               | ISET2P Error Amplifier Transconductance                                                         |                                                                                                                                                                                                                                        |             |                                                            | 0.8                                                        |                                                            | ms                                     |

| R <sub>VC2</sub>                                                   | VC2 Output Impedance                                                                            |                                                                                                                                                                                                                                        |             |                                                            | 1000                                                       |                                                            | kΩ                                     |

| ΔI <sub>SET1P</sub>                                                | Buck Mode Input Current (ISET1P) Regulation<br>Error (Note 15)                                  | $R_{SNS1}$ = 5 $\Omega,~R_{SET1P}$ = 24.3k, $V_{CM1}$ = 48V, DRXN = 2V (Buck Mode)                                                                                                                                                     | •           |                                                            | 0                                                          | ±2.5                                                       | %                                      |

| SYMBOL                       | PARAMETER                                                        | CONDITIONS                                                                                                                                                                  |   | MIN             | TYP              | MAX              | UNITS             |

|------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|------------------|------------------|-------------------|

| ΔI <sub>SET2P</sub>          | Buck Mode Output Current (ISET2P)<br>Regulation Error (Note 15)  | $\label{eq:RSNS2} \begin{array}{l} R_{SNS2} = 5\Omega,  R_{SET2P} = 24.3 \text{k},  V_{CM2} = 14 \text{V}, \\ DRXN = 2 \text{V} \left(Buck Mode\right) \end{array}$         | • |                 | 0                | ±2.5             | %                 |

| ΔI <sub>SHAREBUCK</sub>      | Buck Mode Output Current Sharing Error (Note 16)                 | $ \begin{array}{l} R_{SNS2} = 5\Omega, \ R_{SET2P} = 24.3 \text{K}, \ V_{CM2} = 14 \text{V}, \\ DRXN = 2 \text{V} \ (Buck Mode), \ I_{SHARE} = 0.605 \text{V} \end{array} $ | • |                 | 0                | ±4               | %                 |

| Boost Voltage a              | nd Current Regulation                                            |                                                                                                                                                                             |   |                 |                  |                  |                   |

| V <sub>FB1</sub>             | FB1 Regulation Voltage (Note 13)                                 |                                                                                                                                                                             | • | 1.198           | 1.210            | 1.222            | V                 |

| I <sub>FB1</sub>             | FB1 Pin Bias Current                                             |                                                                                                                                                                             | • |                 | 10               | 50               | nA                |

| gmFB1                        | V1 Error Amplifier Transconductance                              |                                                                                                                                                                             |   |                 | 0.8              |                  | ms                |

| V <sub>ISET1N</sub>          | ISET1N Regulation Voltage (Note 14)                              |                                                                                                                                                                             | • | 1.198           | 1.210            | 1.222            | V                 |

| <b>g</b> mISET1N             | ISET1N Error Amplifier Transconductance                          |                                                                                                                                                                             |   |                 | 0.8              |                  | ms                |

| V <sub>ISET2N</sub>          | ISET2N Regulation Voltage (Note 14)                              |                                                                                                                                                                             | • | 1.198           | 1.210            | 1.222            | V                 |

| <b>9</b> mISET2N             | ISET2N Error Amplifier Transconductance                          |                                                                                                                                                                             |   |                 | 0.8              |                  | ms                |

| R <sub>VC1</sub>             | VC1 Output Impedance                                             |                                                                                                                                                                             |   |                 | 1000             |                  | kΩ                |

| $\Delta I_{SET1N}$           | Boost Mode Output Current (ISET1N)<br>Regulation Error (Note 15) | $ \begin{array}{l} R_{SNS1} = 5\Omega,  R_{SET1N} = 24.3 \text{k},  V_{CM1} = 48 \text{V}, \\ DRXN = 2 \text{V} \left( Buck Mode \right) \end{array} $                      | • |                 | 0                | ±2.5             | %                 |

| $\Delta I_{SET2N}$           | Boost Mode Input Current (ISET2N)<br>Regulation Error (Note 15)  | $R_{SNS2} = 5\Omega$ , $R_{SET2N} = 24.3k$ , $V_{CM2} = 14V$ , DRXN = 2V (Buck Mode)                                                                                        | • |                 | 0                | ±2.5             | %                 |

| ΔI <sub>SHAREBOOST</sub>     | Boost Mode Output Current Sharing Error<br>(Note 16)             | $R_{SNS1} = 5\Omega$ , $R_{SET1N} = 24.3k$ , $V_{CM1} = 14V$ ,<br>DRXN = 2V (Buck Mode), IS <sub>HARE</sub> = 0.605V                                                        | • |                 | 0                | ±4               | %                 |

| Switching MOS                | FET Driver                                                       |                                                                                                                                                                             |   |                 |                  |                  |                   |

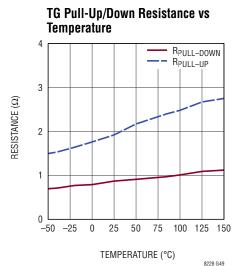

| RTG                          | Pull-Up On-Resistance<br>Pull-Down On-Resistance                 |                                                                                                                                                                             |   |                 | 2.5<br>1.0       |                  | Ω<br>Ω            |

| RBG                          | Pull-Up On-Resistance<br>Pull-Down On-Resistance                 |                                                                                                                                                                             |   |                 | 2.5<br>1.0       |                  | Ω<br>Ω            |

| t <sub>RTG</sub>             | TG Rise Time                                                     | C <sub>LOAD</sub> = 6800pF (10% to 90%)                                                                                                                                     |   |                 | 50               |                  | ns                |

| t <sub>FTG</sub>             | TG Fall Time                                                     | C <sub>LOAD</sub> = 6800pF (10% to 90%)                                                                                                                                     |   |                 | 20               |                  | ns                |

| t <sub>RBG</sub>             | BG Rise Time                                                     | C <sub>LOAD</sub> = 6800pF (10% to 90%)                                                                                                                                     |   |                 | 50               |                  | ns                |

| t <sub>FBG</sub>             | BG Fall Time                                                     | C <sub>LOAD</sub> = 6800pF (10% to 90%)                                                                                                                                     |   |                 | 20               |                  | ns                |

| t <sub>DTGBG</sub>           | TG Off to BG On Delay                                            | C <sub>LOAD</sub> = 6800pF Each Driver (50% to 50%)                                                                                                                         |   |                 | 50               |                  | ns                |

| t <sub>DBGTG</sub>           | BG Off to TG On Delay                                            | C <sub>LOAD</sub> = 6800pF Each Driver (50% to 50%)                                                                                                                         |   |                 | 50               |                  | ns                |

| t <sub>ONBUCK</sub>          | Min TG On-Time in Buck Mode                                      | DRXN = 2V                                                                                                                                                                   |   |                 | 150              |                  | ns                |

| t <sub>ONBOOST</sub>         | Min BG On-Time in Boost Mode                                     | DRXN = 0V                                                                                                                                                                   |   |                 | 150              |                  | ns                |

| t <sub>OFFBOOST</sub>        | Min BG Off-Time in Boost Mode                                    | DRXN = 0V                                                                                                                                                                   |   |                 | 200              |                  | ns                |

| t <sub>DTGBG,V1D = 48V</sub> | TG Off to BG On Delay, V <sub>1D</sub> = 48V (Note 17)           |                                                                                                                                                                             |   |                 | 60               |                  | ns                |

| t <sub>DTGBG,V1D =100V</sub> | TG Off to BG On Delay, V <sub>1D</sub> = 100V (Note 17)          |                                                                                                                                                                             |   |                 | 60               |                  | ns                |

| PLL and Oscilla              | tor                                                              | 1                                                                                                                                                                           |   |                 |                  |                  |                   |

| f <sub>PROG</sub>            | Programmable Frequency                                           | R <sub>RT</sub> = 124k<br>R <sub>RT</sub> = 100k<br>R <sub>RT</sub> = 14k                                                                                                   | • | 75<br>95<br>540 | 80<br>100<br>600 | 85<br>105<br>660 | kHz<br>kHz<br>kHz |

| f <sub>SYNC</sub>            | Synchronizable Frequency                                         |                                                                                                                                                                             | • | 82              |                  | 700              | kHz               |

| f <sub>SPSC,MAX</sub>        | Spread Spectrum Maximum Frequency                                | R <sub>RT</sub> = 100k, f <sub>PROG</sub> = 100kHz                                                                                                                          | • |                 | 130              | 145              | kHz               |

| f <sub>SPSC,MIN</sub>        | Spread Spectrum Maximum Frequency                                | $R_{\text{BT}} = 100$ k, f <sub>PROG</sub> = 100kHz                                                                                                                         |   | 65              | 80               |                  | kHz               |

#### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . DS1 = V1D = 48V, DS2 = BIAS = 14V,  $R_{IN1} = 1k$ ,  $R_{IN2} = 1k$ , and ISHARE = INTV<sub>CC</sub> unless otherwise specified.

| SYMBOL                | PARAMETER                                    | CONDITIONS                                 |   | MIN | ТҮР | MAX  | UNITS |

|-----------------------|----------------------------------------------|--------------------------------------------|---|-----|-----|------|-------|

| Logic                 |                                              |                                            |   |     |     |      |       |

| V <sub>FAULT</sub>    | FAULT Low Voltage                            | I <sub>FAULT</sub> = 2mA (Fault Condition) | • |     | 0.2 | 0.35 | V     |

| ILKGFAULT             | FAULT Pin Leakage Current                    |                                            | • |     |     | 1    | μA    |

| VREPORT               | REPORT Low Voltage                           | I <sub>REPORT</sub> = 2mA                  | • |     | 0.2 | 0.35 | V     |

| ILKGREPORT            | REPORT Pin Leakage Current                   |                                            | • |     |     | 1    | μA    |

| I <sub>PULLDRXN</sub> | DRXN Pin Pull-Down Current (Boost Mode)      | UV1 = 0V                                   | • |     | 100 | 120  | μA    |

| I <sub>LKGDRXN</sub>  | DRXN Pin Leakage Current (Buck Mode)         |                                            | • |     |     | 1    | μA    |

| R <sub>IGND</sub>     | IGND Pin Resistance to GND (Sharing Enabled) |                                            | • |     | 120 | 200  | Ω     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for an extended period may affect device reliability and lifetime.

**Note 2:** An internal clamp limits the DG1 pin to a minimum of 10V above DS1. Driving this pin to voltages beyond this clamp may damage the device.

**Note 3:** An internal clamp limits the DG2 pin to a minimum of 10V above DS2. Driving this pin to voltages beyond this clamp may damage the device.

**Note 4:** Negative voltages on the SW pin are limited in an application by the body diodes of the external NMOS device M3, or parallel Schottky diodes when present. The SW pin is tolerant to these negative voltages in excess of one diode drop below ground down to –5V, guaranteed by design.

Note 5: No external loading is allowed on this pin other than for charging the boost capacitor,  $C_{BST}$ .

**Note 6:** Do not apply a voltage or current sources to these pins. They must be connected to capacitive loads only, otherwise permanent damage may occur.

**Note 7:** INTV<sub>CC</sub> cannot be externally driven. No external loading is allowed on this pin other than connecting to the ISHARE pin and the pull-up resistor for DRXN whose value should not be less than 50k.

**Note 8:** The LT8228 is tested and specified under pulse load conditions such that  $T_J \cong T_A$ . The LT8228E is 100% production tested at  $T_A = 25^{\circ}$ C and performance is guaranteed from 0°C to 125°C. Performance at -40°C to 125°C is assured by design, characterization and correlation with statistical process controls. The LT8228I is guaranteed over the full -40°C to 125°C operating junction temperature range. The LT8228H is guaranteed over the full -40°C to 150°C operating junction temperature range.

**Note 9:** The LT8228 includes over-temperature protection that is intended to protect the device during overload conditions. When the junction temperature exceeds 150°C, overtemperature protection is activated. Continuous operation above the specified maximum operating junction temperature may impair device reliability or permanently damage the device.

**Note 10:** Current convention. Positive current is defined as current flowing out of the pin.

**Note 11:** There is a direct conduction path from V<sub>2</sub> to V<sub>1D</sub> through V<sub>2</sub> protection MOSFET M4 and the body diode of TG MOSFET M2. In Boost mode, this specification limits the current into V<sub>1</sub> from V1D through DG1.

**Note 12:**  $I_{B1}$  is defined as the average of the input bias current to the SNS1P and SNS1N pins. Likewise,  $I_{B2}$  is defined as the average of the input bias current to the SNS2P and SNS2N pins. The LT8228 is tested and specified for these conditions with the voltages at the SNS1P, SNS1N, SNS2P and SNS2N pins applied through 1k input gain resistors.  $V_{RSNS1}$  represents the voltage between the input gain resistors for the SNS1P and SNS1N pins. Likewise,  $V_{RSNS2}$  represents the voltage between the input gain resistors for the SNS1P and SNS1N pins. Likewise,  $V_{RSNS2}$  represents the voltage between the input gain resistors for the SNS2P and SNS2N pins.  $V_{CM1}$  and  $V_{CM2}$  are the common mode voltages at the input gain resistors  $R_{IN1}$  and  $R_{IN2}$ .

**Note 13:** The LT8228 is tested in a feedback loop that servos the output of the error amplifier, VC, to the internal reference voltage by tying the FB pin to the VC pin with all ISET pins tied to ground.

**Note 14:** The LT8228 is tested in a feedback loop that servos the output of the error amplifier VC to the internal reference voltage by tying the ISET pin under test to the VC pin with the FB and other ISET pins tied to ground.

**Note 15:** Current regulation error is the difference between the measured current through the sense resistor and the programmed current set by: (1) the sense resistor  $R_{SNS}$ , (2) the input gain resistors  $R_{IN}$  and (3) the ISET resistor  $R_{SET}$ . The LT8228 is tested in a feedback loop that regulates a current through  $R_{SNS}$  by tying the VC pin to the gate of a grounded N-channel MOSFET whose drain is connected to  $R_{SNS}$ . The error due to the SNS pin bias current across  $R_{SNS}$  is subtracted from this specification. This specification is tested with no ripple voltage on  $R_{SNS}$ .

**Note 16:** Current sharing error is the difference between the current through the sense resistor  $R_{SNS}$  and the average current defined by the ISHARE pin. The voltage on ISHARE represents the average ISHARE currents of multiple ideal LT8228s in parallel. The LT8228 is tested in a feedback loop that regulates a current through  $R_{SNS}$  by tying the VC pin to the gate of a grounded N-channel MOSFET whose drain is connected to  $R_{SNS}$ . The current sharing loop servos the ISET1N pin voltage in boost mode or the ISET2P pin voltage in buck mode to the ISHARE pin voltage of 600mV. The error due to the SNS pin bias current across  $R_{SNS}$  is subtracted from this specification. This specification is tested with no ripple voltage on  $R_{SNS}$ .

**Note 17:** Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels. Rise and fall times are assured by design, characterization and correlation with statistical process controls.

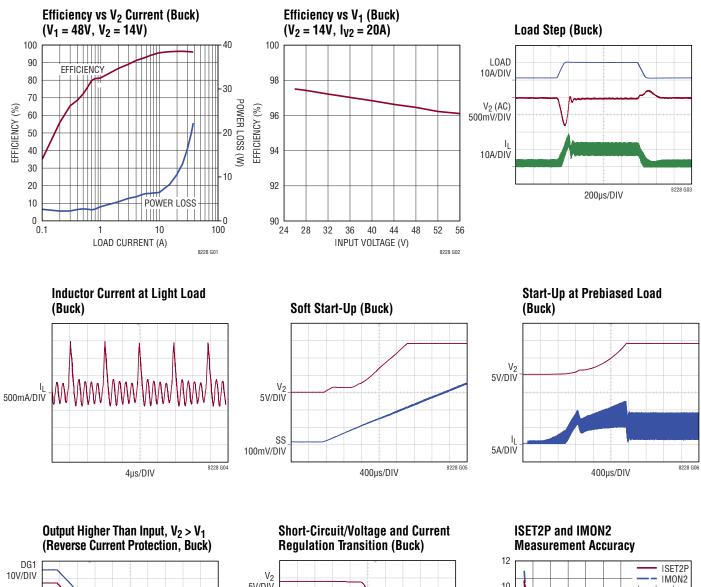

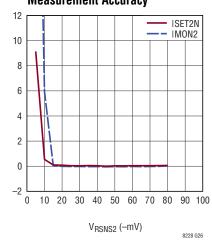

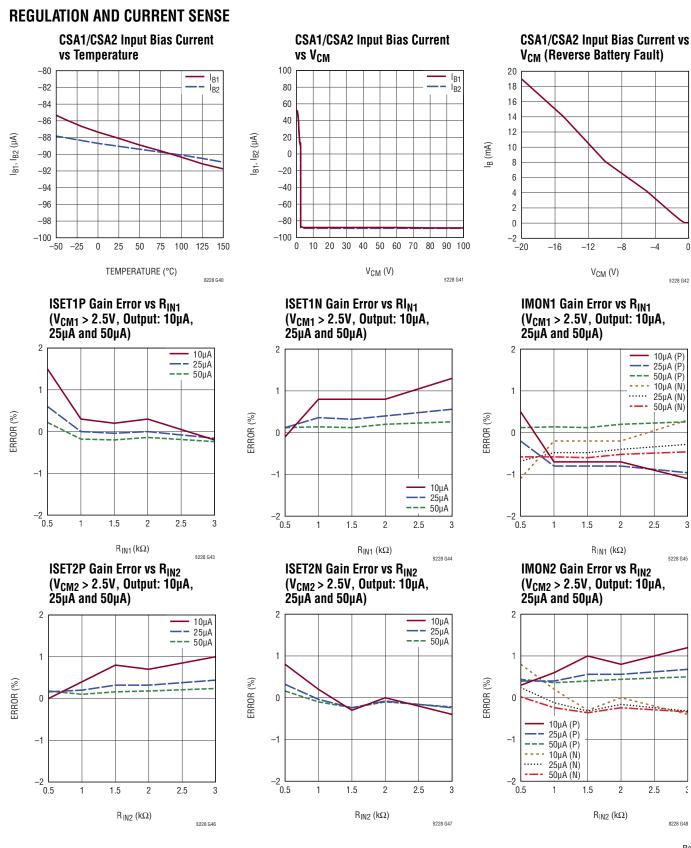

#### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

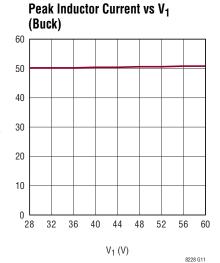

#### **BUCK EFFICIENCY AND OPERATION**

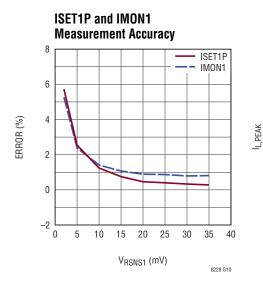

ERROR (%)

8228 G09

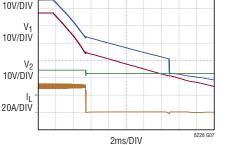

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

#### **BUCK EFFICIENCY AND OPERATION**

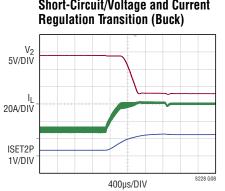

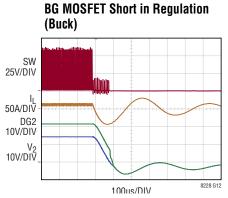

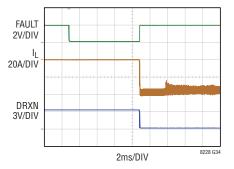

#### TG MOSFET Short in Regulation (Buck)

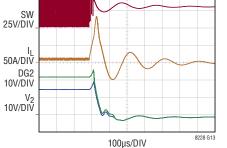

## Reverse Battery Insertion at V<sub>2</sub> (LT8228 Disabled)

## Reverse Battery Insertion at $\ensuremath{V_2}$ in Regulation

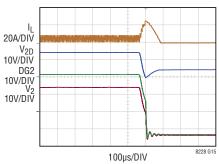

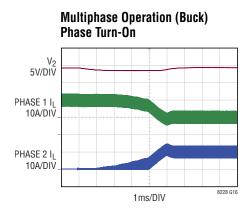

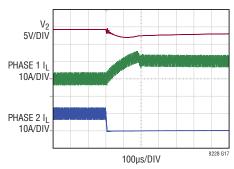

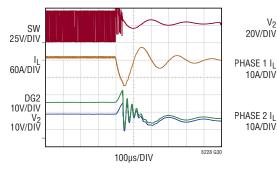

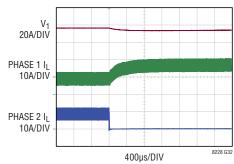

#### Multiphase Operation (Buck) Phase Turn-Off

#### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

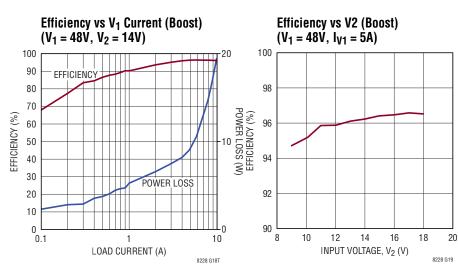

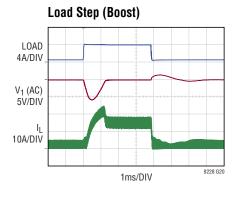

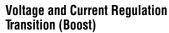

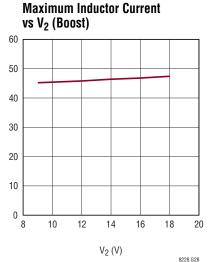

#### **BOOST EFFICIENCY AND OPERATION**

Output Short (Boost, Start-Up)

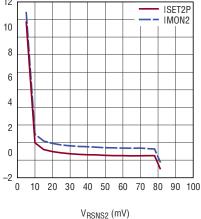

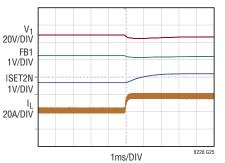

**ISET2N and IMON2** Measurement Accuracy

ERROR (%)

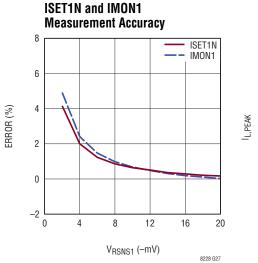

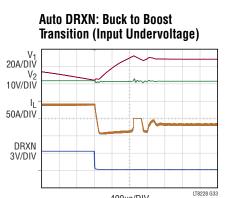

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^{\circ}C$ , unless otherwise noted.

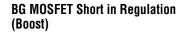

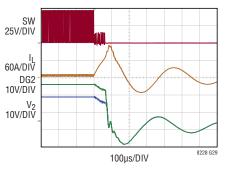

#### **BOOST EFFICIENCY AND OPERATION**

**TG MOSFET Short in Regulation** (Boost)

4ms/DIV

400µs/DIV

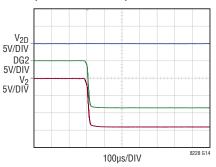

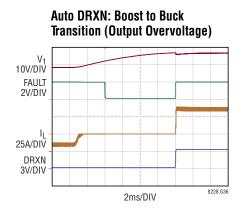

Auto DRXN: Buck to Boost Transition (Output Overvoltage)

8228 G31

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

#### **BOOST EFFICIENCY AND OPERATION**

#### ENABLE, SUPPLY CURRENT AND V<sub>CC</sub>

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

3

0

3

### TYPICAL PERFORMANCE CHARACTERISTICS

#### SS CURRENT, FREQUENCY, THRESHOLDS AND DRIVER

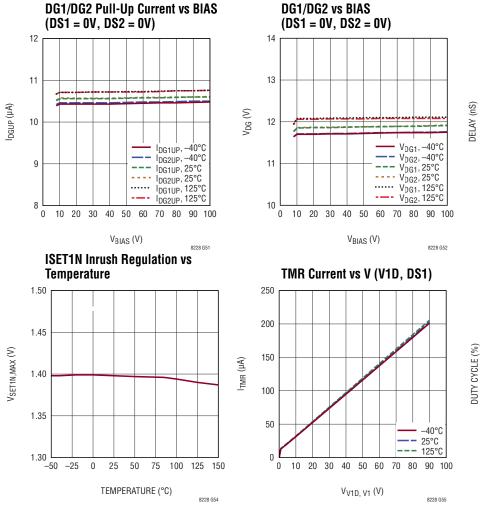

#### **PROTECTION MOSFET CONTROLLER**

BG Pull-Up/Down Resistance vs Temperature 4 R<sub>PULL-DOWN</sub> R<sub>PULL\_UP</sub> 3 2 1 0 -25 -50 0 25 50 75 100 125 150 TEMPERATURE (°C) 8228 650

RESISTANCE (Ω)

$T_A = 25^{\circ}C$ , unless otherwise noted.

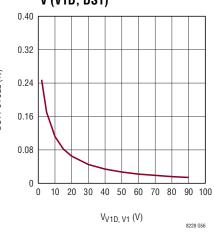

#### DG1/DG2 Turn-Off Delay vs Capacitance

C<sub>DG</sub> (nF) DG1 Retry Duty Cycle vs V (V1D, DS1)

Rev. A

8228 G53

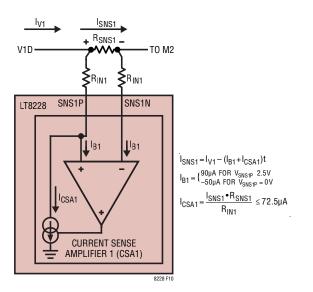

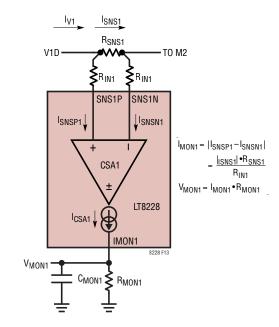

**SNS1P, SNS1N (Pins 1, 2):** Positive and Negative Input Terminals of the V<sub>1</sub> Bidirectional Current Sense Amplifier (CSA1 in the Block Diagram section). The pins allow current monitoring and regulation of the V<sub>1</sub> input current in buck mode and V<sub>1</sub> output current in boost mode. Current sense polarity is positive for current flowing out of V<sub>1</sub> into V<sub>2</sub>. Place input gain resistors R<sub>IN1</sub> between the current sense resistor R<sub>SNS1</sub> and these pins. Typical bias current into these pins is 90µA for common mode voltage above 2.5V. As common mode voltage decreases below 2.5V, bias current decreases and reverses direction. Refer to the curve of I<sub>B1</sub> over V<sub>CM1</sub> in the Typical Performance Characteristics section.

CSA1 is connected in a negative feedback loop to make SNS1N and SNS1P pin voltages equal. The voltage across the current sense resistor and the input gain resistors generates a difference in current flowing into the SNS1N and SNS1P pins,  $I_{SNS1N}$  and  $I_{SNS1P}$ . The current flowing through  $R_{SNS1}$ ,  $I_{SNS1}$ , includes the  $V_1$  current, the input bias current of CSA1's negative feedback terminal and the differential current given by Equation 1.

$$I_{SNS1N} - I_{SNS1P} = \frac{I_{SNS1} \bullet R_{SNS1}}{R_{IN1}}$$

(1)

In buck mode, this current difference is generated out of the ISET1P and IMON1 pins. In boost mode, it is generated out of the ISET1N, ISHARE and IMON1 pins. Limit the difference between SNS1N and SNS1P pin currents to  $\pm 100\mu$ A by choosing the values of R<sub>SNS1</sub> and R<sub>IN1</sub> appropriately. Refer to the R<sub>SNS1</sub> and R<sub>IN1</sub> Selection in Applications Information section for more details.

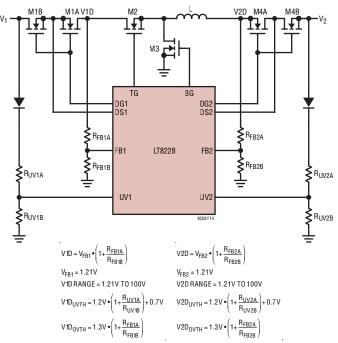

**UV1 (Pin 3):** Undervoltage Detection Input for  $V_1$ . It is a high impedance pin with the undervoltage detection threshold set at 1.2V typically. The undervoltage level is set using a resistor divider connected between  $V_1$  node and ground. If  $V_1$  needs reverse voltage protection, connect the resistor divider in series with a diode whose anode is connected to  $V_1$ . The status of the UV1 pin is reported at the REPORT pin in buck mode.

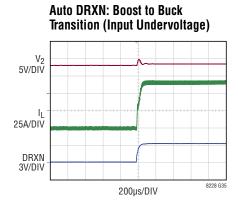

If the DRXN pin is externally set high for buck mode operation and the UV1 pin voltage falls below its threshold voltage, the FAULT and SS pins pull low and the LT8228 stops switching. If the DRXN pin is high but not externally controlled, and the UV1 pin voltage falls below the threshold voltage, the regulation mode changes from buck to boost and the DRXN pin is internally driven low. See the Operation section for more information. Tie the pin to  $INTV_{CC}$  if not used.

**FB1 (Pin 4):**  $V_{1D}$  Feedback Voltage and Overvoltage Detection Input. This pin is one of the boost mode error amplifier's (EA1 in the Block Diagram section) inverting terminals. It is a high impedance pin and senses the  $V_{1D}$  voltage through an external resistor divider network. The pin is regulated to the typical internal reference voltage of 1.21V in boost mode.

V1D overvoltage detection threshold is set at 1.3V typically. The status of  $V_{1D}$  overvoltage is reported at the REPORT pin in boost mode. If the DRXN pin is externally set low for boost mode operation and the FB1 pin voltage rises above its overvoltage threshold voltage, the FAULT pin pulls low. If the DRXN pin is low but not externally controlled, and the FB1 pin voltage rises above the overvoltage threshold voltage for a duration of 1024 switching clock cycle, the regulation mode changes from boost to buck and the DRXN pin is pulled high by the external pullup resistor. Tie the pin to ground if not used.

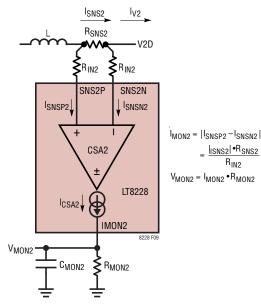

**IMON1 (Pin 5):**  $V_1$  Current Monitor Output. The current out of this pin is equal to the absolute voltage across the current sense resistor  $R_{SNS1}$  divided by the value of the input sense resistor  $R_{IN1}$ . This current represents  $V_1$  input current in buck mode and  $V_1$  output current in boost mode. Connecting a resistor  $R_{MON1}$ , from IMON1 to ground generates a voltage  $V_{MON1}$  for monitoring by an external ADC. The maximum dynamic range for IMON1 is 2.5V. To set  $R_{MON1}$ , first determine the maximum monitor voltage  $V_{MON1MAX}$  based on ADC input dynamic range. Next, calculate the value of  $R_{MON1}$  with Equation 2.

$$R_{MON1} = \frac{R_{IN1}}{I_{SNS1MAX} \bullet R_{SNS1}} \bullet V_{MON1MAX}$$

(2)

where  $I_{SNS1MAX}$  is the maximum of the programmed  $V_1$  output current limit  $I_{V1N(LIM)}$  in boost mode or the programmed  $V_1$  input current limit  $I_{V1P(LIM)}$  in buck mode. A filtering capacitor can be added to read the average current at the ADC input. Refer to the  $R_{MON1}$  Selection for  $V_1$  Current Monitoring in Applications Information section Rev. A

for more detail on resistor and capacitor selection. Tie the pin to ground if not used.

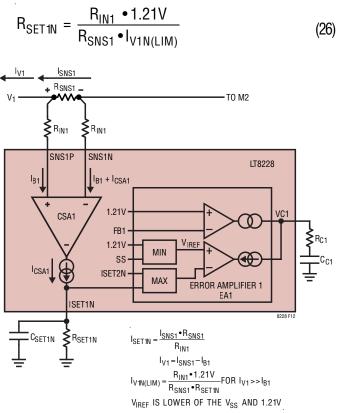

**ISET1N (Pin 6):** Boost Mode Output Current Limit Programming. This pin sets the V<sub>1</sub> output current limit in boost mode by connecting a resistor  $R_{SET1N}$  from ISET1N to ground. The pin outputs a current equal to the negative voltage across the current sense resistor  $R_{SNS1}$  divided by the value of the input sense resistor  $R_{IN1}$ . The voltage at ISET1N is regulated to the lower of the SS pin voltage and the typical internal reference voltage of 1.21V. Calculate the value of  $R_{SET1N}$  with Equation 3.

$$R_{ISET1N} = \frac{R_{IN1}}{R_{SNS1} \bullet I_{V1N(LIM)}} \bullet 1.21V$$

(3)

where  $I_{V1N(LIM)}$  is the maximum programmed  $V_1$  output current limit in boost mode.

In boost mode, at start-up when V<sub>1</sub> is lower than V<sub>2</sub> or V<sub>1</sub> is shorted to GND, the output current cannot be limited by the boost regulation loop. Under such conditions, the LT8228 controls the output current by controlling M1, the V<sub>1</sub> protection MOSFET. The LT8228 controls DG1, the gate of M1 by regulating ISET1N to 1.4V.

Current at this pin is discontinuous during switching. Connect a filtering capacitor at this pin to regulate the average current limit. The value of the filtering capacitor affects the current regulation loop stability. Refer to the  $R_{SET1N}$  Selection for V<sub>1</sub> Output Current Limit (Boost Mode) in Applications Information section for resistor and capacitor selection. Tie the pin to ground if not used.

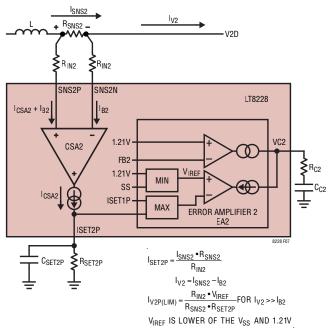

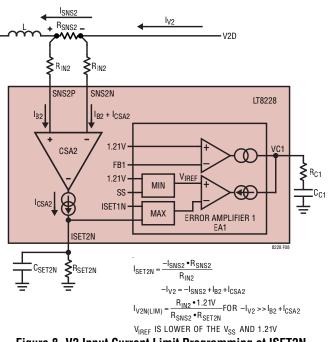

**ISET2N (Pin 7):** Boost Mode Input Current Limit Programming. This pin sets the V<sub>2</sub> input current limit in boost mode by connecting a resistor  $R_{SET2N}$  from ISET2N to ground. The pin outputs a current equal to the negative voltage across the current sense resistor  $R_{SNS2}$  divided by the value of the input sense resistor  $R_{IN2}$ . The voltage at ISET2N is regulated to the lower of the SS pin voltage and the typical internal reference voltage of 1.21V. Calculate the value of  $R_{SET2N}$  with Equation 4.

$$R_{ISET2N} = \frac{R_{IN2}}{R_{SNS2} \bullet I_{V2N(LIM)}} \bullet 1.21V$$

(4)

where  $I_{V2N(LIM)}$  is the maximum programmed  $V_2$  input current limit in boost mode. Connect a filtering capacitor at this pin to regulate the average current limit. The value of the filtering capacitor affects the current regulation loop stability. Refer to the  $R_{SET2N}$  Selection for V2 Input Current Limit (Boost Mode) in Applications Information section for resistor and capacitor selection. Tie the pin to ground if not used.

**VC1 (Pin 8):** Boost Mode Error Amplifier (EA1 in the Block Diagram section) Compensation. VC1 is the compensation pin for boost mode regulation of the  $V_{1D}$  voltage, the  $V_1$  output current and the  $V_2$  input current. EA1 servos the higher of the FB1, ISET1N and ISET2N pin voltages to the typical internal reference voltage of 1.21V. If the SS pin voltage is lower than the typical internal reference of 1.21V, EA1 regulates the current programming pins ISET1N and ISET2N voltages to the SS pin voltage. Leave the pin open if not used.

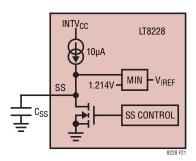

**SS (Pin 9):** Soft-Start Input. The LT8228 limits all the ISET pin voltages to the SS pin voltage when the pin voltage is lower than the typical internal reference voltage of 1.21V. Connect a soft-start capacitor  $C_{SS}$  between the SS pin and ground. When the LT8228 is disabled, or a fault is detected (refer to the Soft-Start in Applications Information section for all the fault conditions), the SS pin is actively pulled low by an internal MOSFET to reset the soft-start. Select  $C_{SS}$  for a soft-start time  $t_{SS}$  according to Equation 5.

$$C_{SS} = \frac{10\mu A}{1.21V} \cdot \frac{1}{t_{SS}}$$

(5)

Leave the pin open if not used.

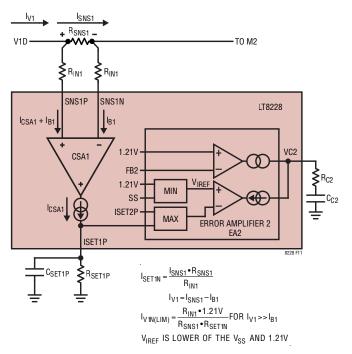

**VC2 (Pin 10):** Buck Mode Error Amplifier (EA2 in the Block Diagram section) Compensation. VC2 is the compensation pin for buck mode regulation of the  $V_{2D}$  voltage, the  $V_2$  output current and the  $V_1$  input current. EA2 servos the higher of the FB2, ISET1P and ISET2P pin voltages to the typical internal reference voltage of 1.21V. If the SS pin voltage is lower than the typical internal reference of 1.21V, EA2 regulates the current programming pins

ISET1P and ISET2P voltages to the SS pin voltage. Leave the pin open if not used.

**ISET1P (Pin 11):** Buck Mode Input Current Limit Programming. This pin sets the V<sub>1</sub> input current limit in buck mode by connecting a resistor  $R_{SET1P}$  from ISET1P to ground. The pin outputs a current equal to the positive voltage across the current sense resistor  $R_{SNS1}$  divided by the value of the input sense resistor  $R_{IN1}$ . The voltage at ISET1P is regulated to the lower of the SS pin voltage and the typical internal reference voltage of 1.21V. Calculate the value of  $R_{SET1P}$  with Equation 6.

$$R_{ISET1P} = \frac{R_{IN1}}{R_{SNS1} \bullet I_{V1P(LIM)}} \bullet 1.21V$$

(6)

where  $I_{V1P(LIM)}$  is the maximum programmed  $V_1$  input current limit in buck mode. Connect a filtering capacitor at this pin to regulate the average current limit. The value of the filtering capacitor affects the current regulation loop stability. Refer to the  $R_{SET1P}$  Selection for  $V_1$  Input Current Limit (Buck Mode) in Applications Information section for resistor and capacitor selection. Tie the pin to ground if not used.

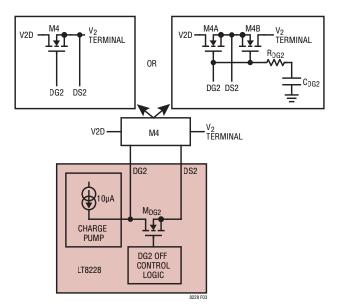

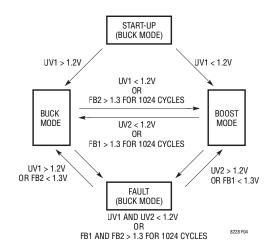

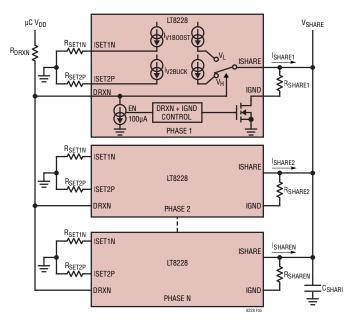

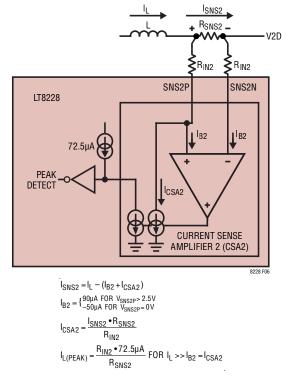

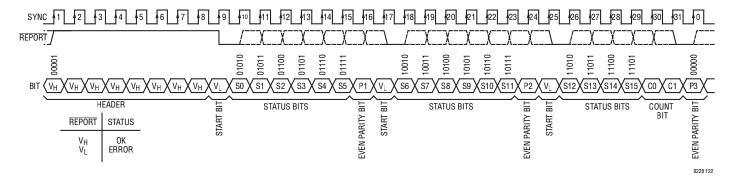

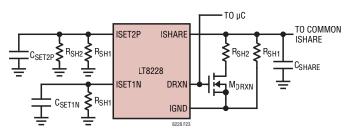

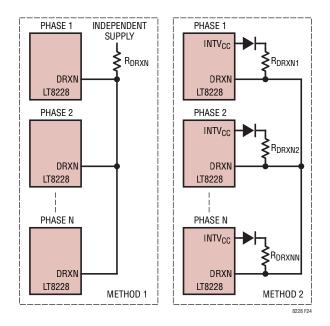

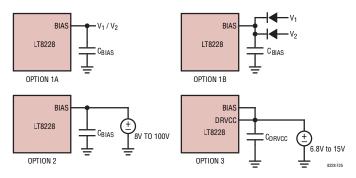

**ISET2P (Pin 12):** Buck Mode Output Current Limit Programming. This pin sets the V<sub>2</sub> output current limit in buck mode by connecting a resistor  $R_{SET2P}$  from ISET2P to ground. The pin outputs a current equal to the positive voltage across the current sense resistor  $R_{SNS2}$  divided by the value of the input sense resistor  $R_{IN2}$ . The voltage at ISET2P is regulated to the lower of the SS pin voltage and the typical internal reference voltage of 1.21V. Calculate the value of  $R_{SET2P}$  with Equation 7.