# MPQ79500FS MPSafe<sup>™</sup> ASIL-D 6-Channel Voltage Monitor, AEC-Q100 Qualified

## DESCRIPTION

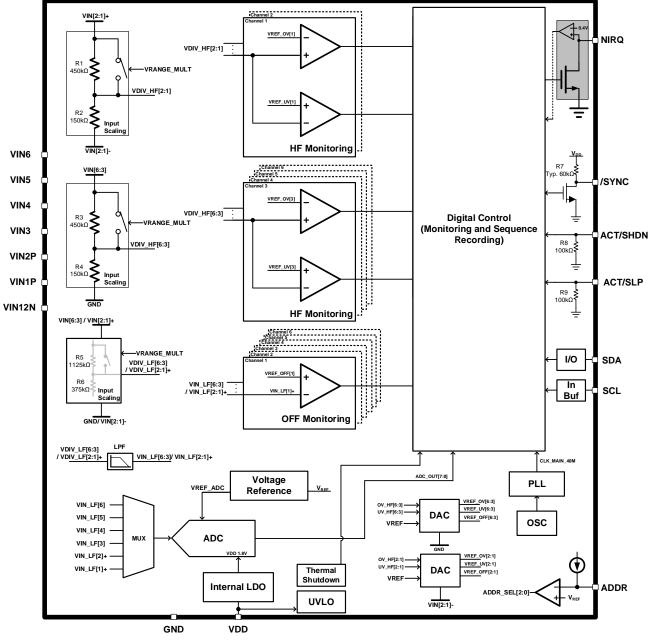

The MPQ79500FS is a 6-channel voltage monitor. It is engineered for automotive applications that require voltage rails to be monitored for safety, such as advanced driver assistance systems (ADAS) and autonomous driving platforms.

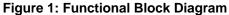

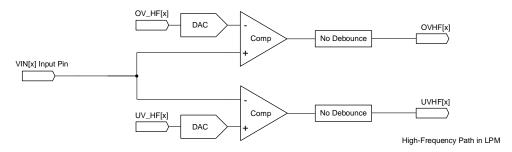

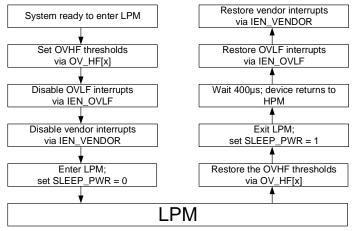

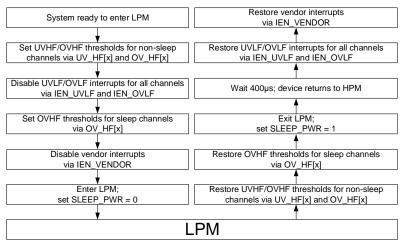

Each voltage monitor input has configurable over-voltage (OV) and under-voltage (UV) thresholds. Highly accurate high-frequency (HF) and low-frequency (LF) voltage monitoring can detect when the voltage thresholds are reached. Two of the inputs are differential, remote voltage sensing input pairs that are wellsuited to monitor voltage rails with high current levels. Low-power mode (LPM) can be enabled to achieve extremely low quiescent currents.

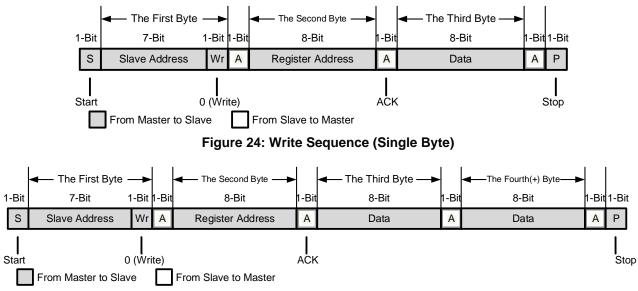

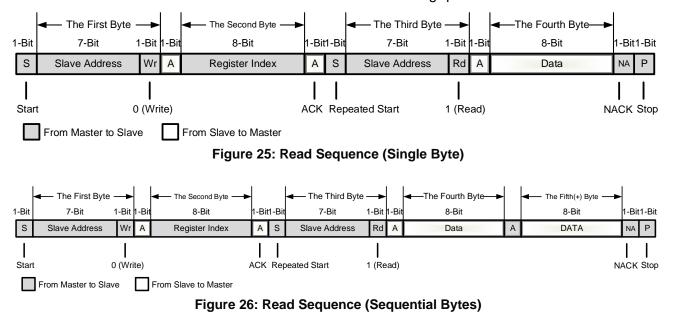

The MPQ79500FS can record the order in which voltage rails are sequenced, as well as their associated timestamps. The device also provides a sync I/O function, which allows multiple devices to be connected together to increase the number of voltage rails that can perform these functions. The device is accessible through an I<sup>2</sup>C interface.

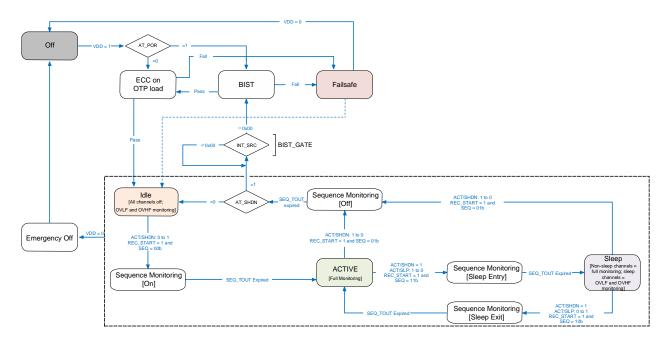

With the integration of sophisticated functional safety features including built-in self-testing (BIST), diagnostics, and write protection, this device is targeted to support applications with a high automotive safety integrity level up to ASIL-D.

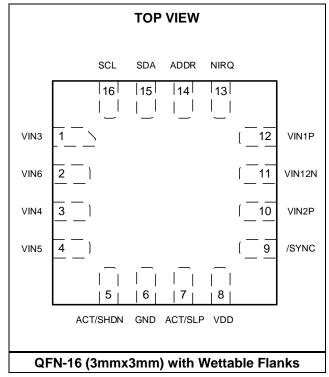

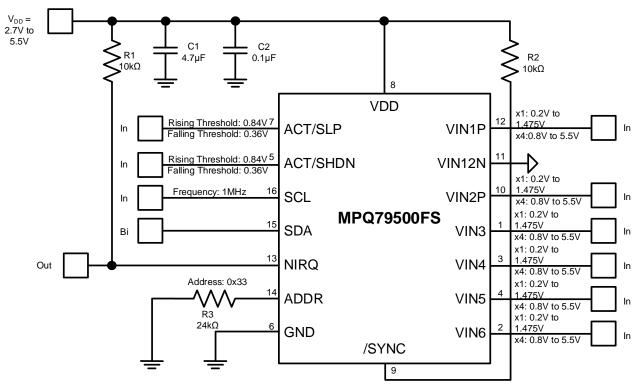

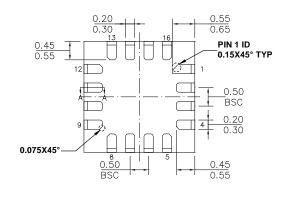

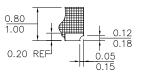

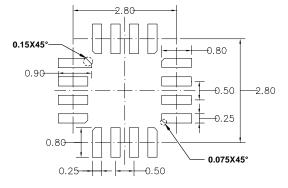

The MPQ79500FS is available in a QFN-16 (3mmx3mm) package with wettable flanks.

# **FEATURES**

- Designed for Automotive ADAS and Autonomous Driving Platforms:

- 2.7V to 5.5V Input Voltage (VIN) Range

- 6 Voltage Monitor Inputs: 4 Single-Ended, 2 Differential

- Absolute OV/UV Thresholds for High-Frequency and Low-Frequency Components:

- 0.2V to 1.475V, 5mV/Step

- 0.8V to 5.5V, 20mV/Step

- High DC Accuracy:

- >1V, ±0.5%

- <1V, ±5mV

- ADC for Voltage-Level Readback

- Selectable High-Power Mode (HPM) and Low-Power Mode (LPM)

- Power Sequence Recording for Power On, Power Off, and Sleep Entry/Exit

- SYNC I/O for Multi-Device Sequence Synchronization

- Write Protection for Critical Registers

- Functional Safety:

- Built-In Self-Testing (BIST)

- Interrupt Output Pin (Fault Reporting)

- Cyclic Redundancy Check (CRC) Protection on Registers

- Support System up to ASIL D

- ISO26262 Functional Safety Certified

- Flexible Application with I<sup>2</sup>C Interface:

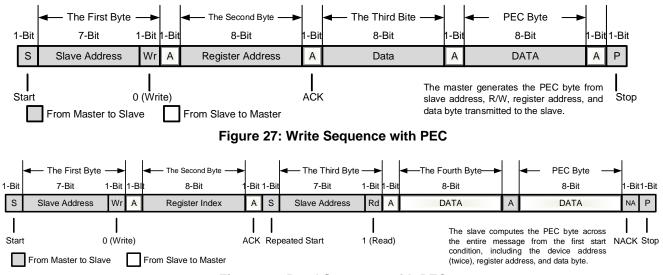

- I<sup>2</sup>C Interface with PEC

- One-Time Programmable (OTP) Memory

- Additional Features:

- Available in a QFN-16 (3mmx3mm)

Package with 0.5mm Pitch and Wettable

Flanks

- Available in AEC-Q100 Grade 1

MPSafe Developed for Functional Safety Applications: ISO26262 Compliant

## APPLICATIONS

- Advanced Driver Assistance Systems (ADAS)

- Autonomous Driving Platforms

- Functional Safety Systems with Multiple Power Rails

- Industrial Robotics

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

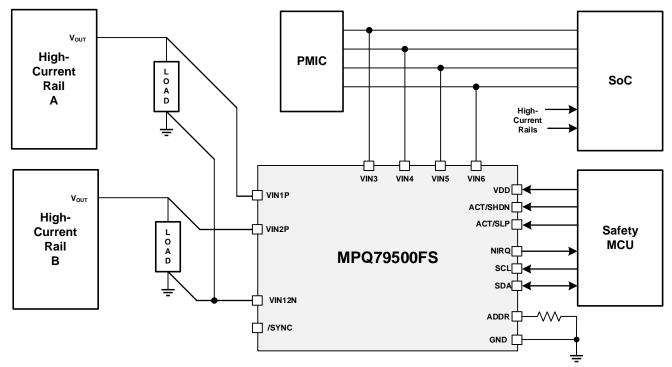

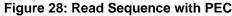

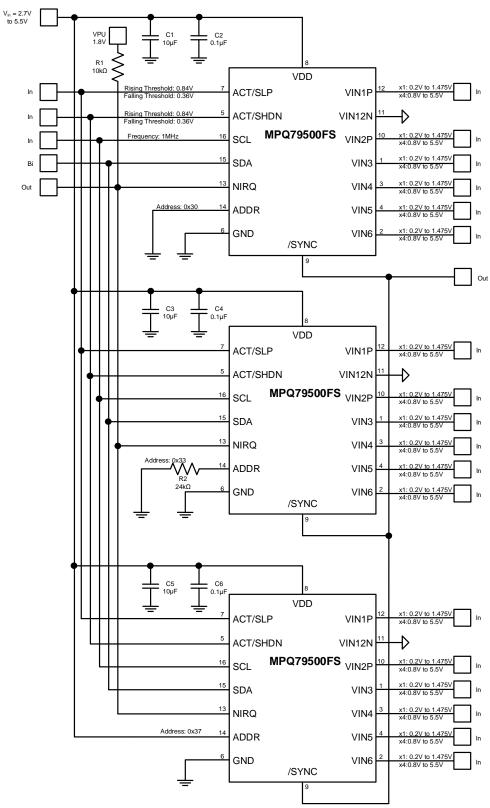

# **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number*              | Package          | Top Marking | MSL Rating*** |  |

|---------------------------|------------------|-------------|---------------|--|

| MPQ79500FSGQE-xxxx-AEC1** | QFN-16 (3mmx3mm) | See Below   | 1             |  |

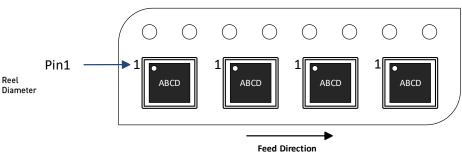

\* For Tape & Reel, add suffix -Z (e.g. MPQ79500FSGQE-xxxx-AEC1-Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the OTP register. Each "x" can be a hexadecimal value between 0 and F. The default device uses the"-0000" code. Contact an MPS FAE to create this unique number.

\*\*\* Moisture Sensitivity Level Rating.

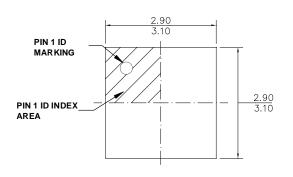

# **TOP MARKING**

BUTY LLLL

BUT: Production code Y: Year code LLLL: Lot number

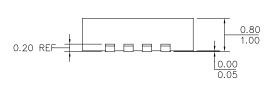

## PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Pin # | Name     | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN3     | Analog In  | Voltage monitor input 3. Connect the VIN3 pin to GND if it is not used.                                                                                                                                                                                                                                                                                                                                                                           |

| 2     | VIN6     | Analog In  | Voltage monitor input 6. Connect the VIN6 pin to GND if it is not used.                                                                                                                                                                                                                                                                                                                                                                           |

| 3     | VIN4     | Analog In  | Voltage monitor input 4. Connect the VIN4 pin to GND if it is not used.                                                                                                                                                                                                                                                                                                                                                                           |

| 4     | VIN5     | Analog In  | Voltage monitor input 5. Connect the VIN5 pin to GND if it is not used.                                                                                                                                                                                                                                                                                                                                                                           |

| 5     | ACT/SHDN | In         | Active/shutdown. The ACT/SHDN pin is the power sequencer control input. Connect ACT/SHDN directly to a voltage or use a resistor (e.g. $10k\Omega$ ). If ACT/SHDN is floating, an internal $100k\Omega$ resistor pulls this pin low. When this pin goes from low (SHDN) to high (ACT), the system starts up. When this pin goes from high (ACT) to low (SHDN), the system shuts down.                                                             |

| 6     | GND      | Supply     | <b>Power ground.</b> Electrically connect the GND pin to the system ground plane with the shortest, lowest-impedance connection possible.                                                                                                                                                                                                                                                                                                         |

| 7     | ACT/SLP  | In         | Active/sleep. The ACT/SLP pin is used in conjunction with the sleep<br>entry/exit sequence control registers. Connect ACT/SLP directly to a voltage<br>or use a resistor (e.g. $10k\Omega$ ). If ACT/SLP is floating, an internal $100k\Omega$<br>resistor pulls this pin low. When this pin goes from low (SLP) to high (ACT),<br>the system exits sleep mode. When this pin goes from high (ACT) to low<br>(SLP), the system enters sleep mode. |

| 8     | VDD      | Supply     | <b>Input supply voltage.</b> To minimize spikes, it is recommended to place a decoupling capacitor from the VDD pin to ground.                                                                                                                                                                                                                                                                                                                    |

| 9     | /SYNC    | In/Out, OD | <b>Sequence monitor synchronization.</b> Float the /SYNC pin or connect it to VDD with a pull-up resistor. For the multiple IC sequence function, connect all of the /SYNC pins together.                                                                                                                                                                                                                                                         |

| 10    | VIN2P    | Analog In  | Voltage monitor input 2 (differential). Connect the VIN2P pin to GND if it is not used. The VIN2P voltage must always exceed the VIN12N voltage.                                                                                                                                                                                                                                                                                                  |

| 11    | VIN12N   | Analog In  | Voltage monitor shared negative input. Do not float the VIN12N pin.                                                                                                                                                                                                                                                                                                                                                                               |

| 12    | VIN1P    | Analog In  | <b>Voltage monitor input 1 (differential).</b> Connect the VIN1P pin to GND if it is not used. The VIN1P voltage must always exceed the VIN12N voltage.                                                                                                                                                                                                                                                                                           |

| 13    | NIRQ     | Out, OD    | <b>Interrupt.</b> The NIRQ pin is an active-low signal. If an event occurs that requires the device status to be read, this pin sends an interrupt output signal to the I <sup>2</sup> C. This pin is an open-drain status pin. Connect NIRQ to an external power supply or VDD with a pull-up resistor.                                                                                                                                          |

| 14    | ADDR     | In         | I <sup>2</sup> C address selection strap.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15    | SDA      | In/Out, OD | <b>I<sup>2</sup>C bus serial data input/output.</b> The SDA pin is an open-drain port. An external pull-up resistor is required to connect this pin to the I <sup>2</sup> C bus supply rail. SDA supports up to 1Mbs of data transfer in fast-mode plus. If this pin is not used, connect it to the VDD pin through a resistor (e.g. 100k $\Omega$ ).                                                                                             |

| 16    | SCL      | In, OD     | <b>I</b> <sup>2</sup> <b>C</b> bus serial clock input. The SCL pin is an open-drain port. An external pull-up resistor is required to connect this pin to the I <sup>2</sup> C bus supply rail. SCL supports up to 1Mbs of data transfer in fast-mode plus. If this pin is not used, connect it to the VDD pin through a resistor (e.g. 100kΩ).                                                                                                   |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| All pins                                       | 0.3V to +6V          |

|------------------------------------------------|----------------------|

| Continuous power dissipation (T <sub>A</sub> = | 25°C) <sup>(2)</sup> |

| QFN-16 (3mmx3mm)                               | 2.4W                 |

| Junction temperature                           | 150°C                |

| Lead temperature                               | 260°C                |

| Storage temperature                            | °C to +150°C         |

## ESD Ratings

Human body model (HBM).....Class 2 <sup>(3)</sup> Charged device model (CDM)...... Class C2b <sup>(4)</sup>

### **Recommended Operating Conditions**

Supply voltage (V\_DD) .....2.7V to 5.5V Operating junction temp (T\_J) .... -40°C to +150°C

*Thermal Resistance* <sup>(5)</sup> *θ*<sub>JA</sub> *θ*<sub>JC</sub> *θ*<sub>JB</sub> QFN-16(3mmx3mm)......52....6.5....7...°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX) -  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on JESD51-7, 4-layer PCB. The value given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

Typical values are at  $V_{DD} = 3.3V$ ,  $T_J = 25$ °C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{DD} = 3.3V$ ,  $T_J = -40$ °C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameters                                                                                                                                  | Symbol                            | Condition                                                                                           | Min  | Тур   | Max  | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|-------|

| VDD Supply                                                                                                                                  |                                   |                                                                                                     |      |       |      |       |

| Supply voltage                                                                                                                              | V <sub>DD</sub>                   |                                                                                                     | 2.7  | 3.3   | 5.5  | V     |

| VDD under-voltage lockout<br>(UVLO) rising threshold                                                                                        | V <sub>UVLO_TH-R</sub>            |                                                                                                     | 2.6  | 2.8   | 3.0  | V     |

| VDD UVLO falling threshold                                                                                                                  | VUVLO_TH -F                       |                                                                                                     | 2.4  | 2.5   | 2.7  | V     |

| V <sub>IN</sub> UVLO threshold<br>hysteresis                                                                                                | VUVLO_HYS                         |                                                                                                     |      | 300   |      | mV    |

| VDD supply current                                                                                                                          | lα                                | HPM                                                                                                 |      | 6     | 8    | mA    |

| (quiescent)                                                                                                                                 | IQ                                | LPM                                                                                                 |      | 560   | 690  | μA    |

| ACT/SHDN, ACT/SLP                                                                                                                           | •                                 |                                                                                                     |      |       |      |       |

| Input logic high                                                                                                                            | VIH                               | V <sub>IH</sub> of 3.3V and 1.8V/1.2V                                                               | 0.84 |       |      | V     |

| Input logic low                                                                                                                             | VIL                               | V <sub>IL</sub> of 3.3V and 1.8V/1.2V                                                               |      |       | 0.36 | V     |

| Enable input pull-down<br>resistor                                                                                                          | R <sub>PD</sub>                   | Enable input pull-down to<br>ensure a safe state in case of<br>an open circuit on the enable<br>pin |      | 100   |      | kΩ    |

| VINx Monitoring                                                                                                                             | -                                 |                                                                                                     |      |       |      | -     |

| VINx input load current                                                                                                                     | I <sub>VIN</sub>                  |                                                                                                     |      | 12    | 20   | μA    |

| Monitoring voltage minimum                                                                                                                  | V <sub>LP_MIN</sub>               | No scaling                                                                                          |      | 0.2   |      | V     |

| threshold (low-frequency<br>channel)                                                                                                        | VLP_MIN_X4                        | With x4 scaling                                                                                     |      | 0.8   |      | V     |

| Monitoring voltage maximum                                                                                                                  | VLP_MAX                           | No scaling                                                                                          |      | 1.475 |      | V     |

| threshold (low-frequency<br>channel)                                                                                                        | V <sub>LP_MAX_X4</sub>            | With x4 scaling                                                                                     |      | 5.5   |      | V     |

| Monitoring voltage minimum                                                                                                                  | VHP_MIN                           | No scaling                                                                                          |      | 0.2   |      | V     |

| threshold <sup>(6)</sup> (high-frequency channel)                                                                                           | VHP_MIN_X4                        | With x4 scaling                                                                                     |      | 0.8   |      | V     |

| Monitoring voltage maximum                                                                                                                  | V <sub>HP_MAX</sub>               | No scaling                                                                                          |      | 1.475 |      | V     |

| threshold <sup>(6)</sup> (high-frequency channel)                                                                                           | VHP_MAX_X4                        | With x4 scaling                                                                                     |      | 5.5   |      | V     |

| Threshold granularity setting                                                                                                               | LSB⊤                              | No scaling                                                                                          |      | 5     |      | mV    |

|                                                                                                                                             | LSBT_X4                           | With x4 scaling                                                                                     |      | 20    |      | mV    |

| Low-pass filter (LPF) cutoff<br>for low-frequency<br>channel thresholds <sup>(6)</sup>                                                      | f <sub>LF</sub>                   | Range of configurable values through the FC_LF[N] register                                          | 250  | 1000  | 4000 | Hz    |

| LPF cutoff for high-<br>frequency<br>channel thresholds <sup>(6)</sup>                                                                      | fнғ                               |                                                                                                     |      |       | 4    | MHz   |

| DC ( <flf) td="" voltage<=""><td></td><td>No scaling, <math>T_J = 25^{\circ}C</math></td><td>-1</td><td>0</td><td>1</td><td>LSB</td></flf)> |                                   | No scaling, $T_J = 25^{\circ}C$                                                                     | -1   | 0     | 1    | LSB   |

| measurement accuracy (low-<br>frequency channel) with no<br>scaling                                                                         | $V_{\text{LP}\_\Delta\text{ERR}}$ | No scaling,<br>T」= -40°C to +150°C                                                                  | -2   | 0     | +2   | LSB   |

| DC ( <f<sub>LF) voltage<br/>measurement accuracy (low<br/>frequency channel) with x4<br/>scaling</f<sub>                                    | $V_{LP\_\Delta ERR\_X4}$          | With x4 scaling                                                                                     | -1   | 0     | +2   | LSB   |

# ELECTRICAL CHARACTERISTIC (continued)

Typical values are at  $V_{DD} = 3.3V$ ,  $T_J = 25$ °C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{DD} = 3.3V$ ,  $T_J = -40$ °C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameters                                                          | Symbol                 | Condition                                                                 | Min  | Тур | Max  | Units |

|---------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------|------|-----|------|-------|

| DC(f, f) values measurement                                         |                        | >1V, T <sub>J</sub> = 25°C                                                | -0.5 | 0   | +0.5 | %     |

| DC (>f <sub>HF</sub> ) voltage measurement accuracy (high-frequency | VHP_derr               | >1V, T <sub>J</sub> = -40°C to +150°C                                     | -1   | 0   | +1   | %     |

| channel) with no scaling <sup>(7)</sup>                             | V HP_AERR              | <1V, T <sub>J</sub> = 25°C                                                | -5   | 0   | +5   | mV    |

|                                                                     |                        | $<1V, T_{J} = -40^{\circ}C \text{ to } +150^{\circ}C$                     | -10  | 0   | +10  | mV    |

| DC (>f <sub>HF</sub> ) voltage measurement                          |                        | >1V, TJ = 25°C                                                            | -2   | 0   | +2   | %     |

| accuracy (high-frequency                                            | $V_{HP\_\Delta ERR\_}$ | >1V, T <sub>J</sub> = -40°C to +150°C                                     | -4   | 0   | +4   | %     |

| channel) with x4 scaling $(7)$                                      | X4                     | <1V, T <sub>J</sub> = 25°C                                                | -20  | 0   | +20  | mV    |

| , C                                                                 |                        | <1V, T <sub>J</sub> = -40°C to +150°C                                     | -40  | 0   | +40  | mV    |

| OFF voltage threshold <sup>(8)</sup>                                | Voff                   |                                                                           | 140  |     | +200 | mV    |

| Sequence timestamp range                                            | tseq                   | Time from the ACT/SHDN or<br>ACT/SLP edge to the max<br>timestamp counter | 100  |     |      | ms    |

| Sequence timestamp resolution                                       | t <sub>SEQ_LSB</sub>   | i i i i i i i i i i i i i i i i i i i                                     |      | 50  |      | μs    |

| Full monitoring active from the ACT/SHDN rising edge                | <b>t</b> мол_аст       |                                                                           |      |     | 10   | μs    |

| Sequence tagging active from<br>the ACT/SHDN or ACT/SLP<br>edge     | tseq_act               |                                                                           |      |     | 10   | μs    |

| /SYNC <sup>(9)</sup> (Supports 1.2 V/1.8V,                          | and 3.3V S             | ignaling via DEV_CFG Option)                                              |      |     |      | •     |

| Input high voltage                                                  | VIH_SYNC               | Rising (V⊮ of 3.3V and 1.8V/1.2V)                                         | 0.84 |     |      | V     |

| Input low voltage                                                   | VIL_SYNC               | Falling (V <sub>IL</sub> of 3.3V and 1.8V/1.2V)                           |      |     | 0.36 | V     |

| Internal pull-up resistor                                           | RPU_SYNC               |                                                                           | 25   |     | 100  | kΩ    |

| Output low                                                          | Vol                    | With an external 10kΩ pull-<br>up resistor                                |      |     | 0.01 | V     |

| NIRQ (Open Drain)                                                   |                        |                                                                           |      |     |      |       |

| Output low                                                          | Vol                    | With an external 10kΩ pull-<br>up resistor                                |      |     | 0.01 | V     |

| Fault detection to NIRQ<br>assertion latency                        | <b>t</b> NIRQ          |                                                                           |      |     | 25   | μs    |

| Built-In Self-Testing (BIST)                                        |                        |                                                                           |      |     |      |       |

| POR to ready with BIST                                              | tcfg_wb                | Include BIST, OTP load with<br>error-correction code (ECC)                |      |     | 20   | ms    |

| POR to ready without BIST                                           | tcfg_nb                | Include OTP load with ECC, $T_J = 25^{\circ}C$                            |      |     | 5    | ms    |

| BIST time <sup>(6)</sup>                                            | t <sub>BIST</sub>      | AT_POR = 1 or AT_SHDN                                                     |      |     | 15   | ms    |

| Clocking                                                            |                        |                                                                           |      |     |      |       |

| Internal clock accuracy                                             | Acciclk                | Clock used for timestamp<br>and SYNC pulse                                | -5   |     | +5   | %     |

| Thermal Shutdown                                                    | 1                      | ·                                                                         |      |     |      |       |

| Thermal shutdown                                                    | T <sub>SD</sub>        | Junction temperature rising                                               |      | 170 |      | °C    |

| Thermal shutdown hysteresis                                         | T <sub>SD-HYS</sub>    |                                                                           |      | 20  |      | °C    |

#### Notes:

6) Guaranteed by design and bench characterization. Not tested in production.

7) MPS guarantees the accuracy at a factory-trimmed voltage level according to customer demand.

8) x4 scaling does not apply to the OFF voltage threshold.

9) If power domains other than V<sub>DD</sub> are applied, consider the level-shifting. Otherwise, there may be additional leakage or current injection.

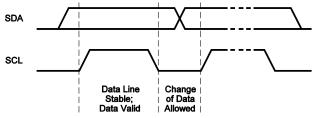

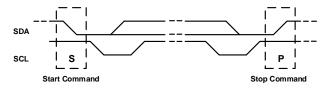

# I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

Typical values are at  $V_{DD} = 3.3V$ ,  $T_J = 25$ °C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{DD} = 3.3V$ ,  $T_J = -40$ °C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameters                                       | Symbol              | Condition                        | Min                           | Тур    | Max  | Units |

|--------------------------------------------------|---------------------|----------------------------------|-------------------------------|--------|------|-------|

| I <sup>2</sup> C Interface Specifications        | (Supports 1.2       | 2V/1.8V, and 3.3V Signaling vi   | ia DEV_CFG                    | Option |      |       |

| Innut logic high (SDA (SCI )                     | Maria               | Rising (VOD = 3.3V)              | 2.0                           |        |      | V     |

| Input logic high (SDA/SCL)                       | VIH_I2C             | Rising (VOD = $1.2V/1.8V$ )      | 0.84                          |        |      | V     |

| Input logic low (SDA/SCL)                        | VIL_I2C             | Falling (VOD = 3.3V)             |                               |        | 0.8  | V     |

| Input logic low (SDA/SCL)                        | VIL_I2C             | Falling (VOD = 1.2V/1.8 V)       |                               |        | 0.36 | V     |

| Output low                                       | V <sub>OL</sub>     | SDA with a 10kΩ pull-up resistor |                               |        | 0.1  | V     |

| Input capacitance                                | Csda, Csdl          | 16515101                         |                               | 5      |      | pF    |

| SCL clock frequency                              | fscL                |                                  |                               |        | 1    | MHz   |

| SCL high time                                    | tніgн               |                                  | 0.26                          |        |      | μs    |

| SCL low time                                     | tLOW                |                                  | 0.5                           |        |      | μs    |

| Data set-up time                                 | tsu_dat             |                                  | 50                            |        |      | ns    |

| Data hold time                                   | thd_dat             |                                  | 0                             |        |      | μs    |

| Set-up time for a repeated start condition       | tsu_sta             |                                  | 0.26                          |        |      | μs    |

| Hold time for start condition                    | t <sub>HD_STA</sub> |                                  | 0.26                          |        |      | μs    |

| Bus free time between a start and stop condition | tBUF                |                                  | 0.5                           |        |      | μs    |

| Set-up time for stop condition                   | tsu,sто             |                                  | 0.26                          |        |      | μs    |

| SCL and SDA rising time                          | t <sub>R</sub>      |                                  | 20 x (V <sub>DD</sub> / 5.5V) |        | 120  | ns    |

| SCL and SDA falling time                         | tF                  |                                  | 20 x (V <sub>DD</sub> / 5.5V) |        | 120  | ns    |

| Suppressed spike pulse width                     | t <sub>SP</sub>     |                                  | 0                             |        | 50   | ns    |

| Capacitance bus for each bus line                | Св                  |                                  |                               |        | 550  | pF    |

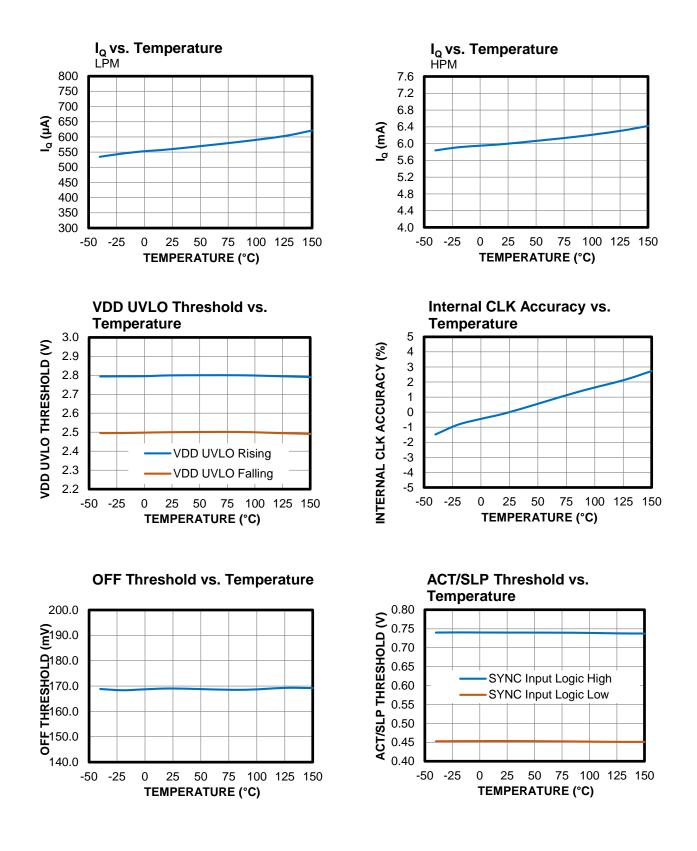

# **TYPICAL CHARACTERISTICS**

$V_{DD}$  = 3.3V,  $T_{J}$  = -40°C to +150°C, unless otherwise noted.

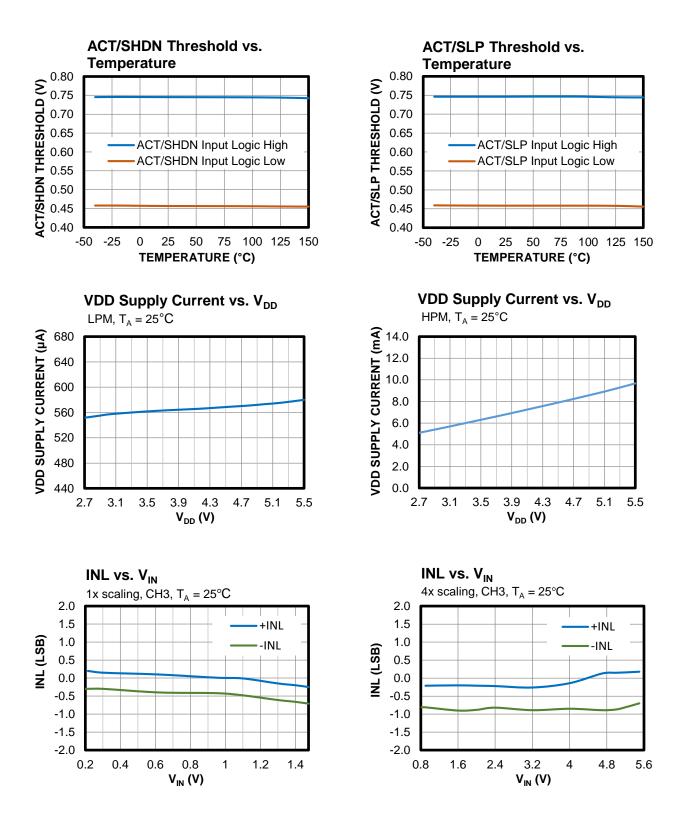

# TYPICAL CHARACTERISTICS (continued)

VDD = 3.3V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{DD}$  = 3.3V, VPU = 3.3V,  $T_A$  = 25°C, unless otherwise noted.

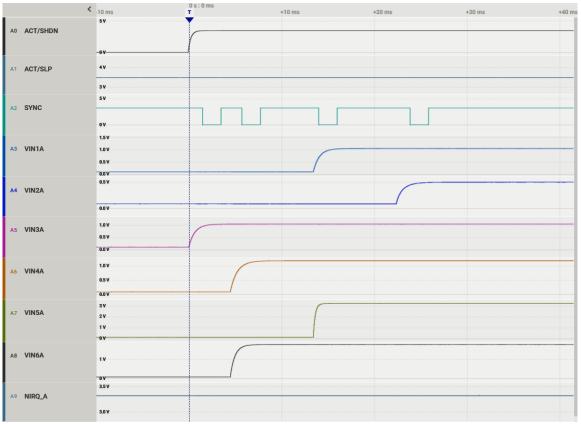

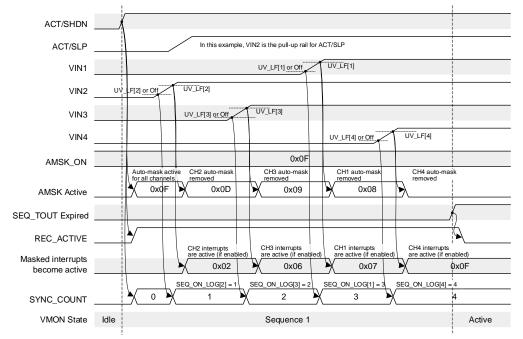

#### **SEQ Monitoring On**

Single MPQ79500FS device, ACT/SHDN = low to high, ACT/SLP = high

#### **Table 1: Read Register after Timeout**

|      | Bank 0 o      | of Part A      |                                                | Bank 1 of Part A |               |                |                                                    |  |

|------|---------------|----------------|------------------------------------------------|------------------|---------------|----------------|----------------------------------------------------|--|

| Add. | Register Name | Read<br>Result | Description                                    | Add.             | Register Name | Read<br>Result | Description                                        |  |

| 0x10 | INT_SRC       | 00             | No interrupt after<br>SEQ is on.               | 0x13             | IEN_UVHF      | 3F             | UVHF monitoring for<br>channels 1–6 is<br>enabled. |  |

| 0x11 | INT_MONITOR   | 00             | No interrupt after<br>SEQ is on.               | 0x14             | IEN_UVLF      | 3F             | UVLF monitoring for<br>channels 1–6 is<br>enabled. |  |

| 0x12 | INT_UVHF      | 00             | No UVHF fault has<br>occurred.                 | 0x15             | IEN_OVHF      | 3F             | OVHF monitoring for<br>channels 1–6 is<br>enabled. |  |

| 0x14 | INT_UVLF      | 00             | No UVLF fault has<br>occurred.                 | 0x16             | IEN_OVLF      | 3F             | OVLF monitoring for<br>channels 1–6 is<br>enabled. |  |

| 0x16 | INT_OVHF      | 00             | No OVHF fault has<br>occurred.                 | 0x17             | IEN_SEQ_ON    | 3F             | SEQ_ON monitoring for channels 1–6 is enabled.     |  |

| 0x18 | INT_OVLF      | 00             | No OVLF fault has<br>occurred.                 | 0x18             | IEN_SEQ_OFF   | 3F             | EQ_OFF for<br>channels 1–6 is<br>enabled.          |  |

| 0x1A | INT_SEQ_ON    | 00             | No power up<br>sequence fault has<br>occurred. | 0x19             | IEN_SEQ_EXS   | 3F             | SEQ_EXS for<br>channels 1–6 is<br>enabled.         |  |

| 0x1C | INT_SEQ_OFF   | 00 | No power off<br>sequence fault has<br>occurred.                                           | 0x20 | UV_HF[1]    | 80 | The channel 1 UVHF threshold is 0.84V.                                                                    |

|------|---------------|----|-------------------------------------------------------------------------------------------|------|-------------|----|-----------------------------------------------------------------------------------------------------------|

| 0x1E | INT_SEQ_EXS   | 00 | No sleep exit<br>sequence fault has<br>occurred.                                          | 0x21 | OV_HF[1]    | D4 | The channel 1 OVHF threshold is 1.26V.                                                                    |

| 0x20 | INT_SEQ_ENS   | 00 | No sleep entry<br>sequence fault has<br>occurred.                                         | 0x22 | UV_LF[1]    | 94 | The channel 1 UVLF threshold is 0.94V.                                                                    |

| 0x22 | NT_CONTROL    | 00 | No interrupt after SEQ is on.                                                             | 0x23 | OV_LF[1]    | C0 | The channel 1 OVLF threshold is 1.16V.                                                                    |

| 0x23 | INT_TEST      | 00 | No interrupt after SEQ is on.                                                             | 0x24 | FLT_HF[1]   | 22 | The OV/UV<br>debouncing time for<br>the high-frequency<br>threshold comparator<br>for channel 1 is 0.4µs. |

| 0x24 | INT_VENDOR    | 00 | No interrupt after SEQ is on.                                                             | 0x25 | FC_LF[1]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 1 is 1kHz.                                      |

| 0x30 | VMON_STAT     | 4E | The monitoring status is as expected.                                                     | 0x32 | UV_LF[2]    | 30 | The channel 2 UVLF threshold is 0.44V.                                                                    |

| 0x31 | TEST_INFO     | 00 | No error for the<br>internal self-testing<br>and ECC.                                     | 0x35 | FC_LF[2]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 2 is 1kHz.                                      |

| 0x32 | OFF_STAT      | 00 | Channels 1–6 are in the on state.                                                         | 0x42 | UV_LF[3]    | 94 | The channel 3 UVLF threshold is 0.94V.                                                                    |

| 0x36 | SEQ_ORD_STAT  | 04 | 4 sync pulse count.                                                                       | 0x45 | FC_LF[3]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 3 is 1kHz.                                      |

| 0x40 | VIN_LVL[1]    | AC | VIN1A is 1.06V in the<br>active state after SEQ<br>on.                                    | 0x52 | UV_LF[4]    | B0 | The channel 4 UVLF threshold is 1.08V.                                                                    |

| 0x41 | VIN_LVL[2]    | 3D | VIN2A is 0.505V in<br>the active state after<br>SEQ on.                                   | 0x55 | FC_LF[4]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 4 is 1kHz.                                      |

| 0x42 | VIN_LVL[3]    | AA | VIN3A is 1.05V in the active state after SEQ on.                                          | 0x62 | UV_LF[5]    | 6C | The channel 5 UVLF threshold is 2.96V.                                                                    |

| 0x43 | VIN_LVL[4]    | C8 | VIN4A is 1.2V in the active state after SEQ on.                                           | 0x65 | FC_LF[5]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 5 is 1kHz.                                      |

| 0x44 | VIN_LVL[5]    | 7B | VIN5A is 3.26V in the active state after SEQ on.                                          | 0x72 | UV_LF[6]    | 29 | The channel 6 UVLF threshold is 1.62V.                                                                    |

| 0x45 | VIN_LVL[6]    | 32 | VIN6A is 1.8V in the<br>active state after SEQ<br>is on.                                  | 0x75 | FC_LF[6]    | 04 | The low-frequency<br>path cutoff frequency<br>for channel 6 is 1kHz.                                      |

| 0x50 | SEQ_ON_LOG[1] | 03 | The rail on VIN1A is<br>up in the first SYNC<br>pulse recording as<br>first sequence log. | 0x1A | IEN_SEQ_ENS | 3F | SEQ_ENS monitoring<br>for channels 1–6 is<br>enabled.                                                     |

| 0x51 | SEQ_ON_LOG[2] | 04 | The rail on VIN2A is<br>up in the fourth SYNC<br>pulse record as fourth<br>sequence log.  | 0x1E | VIN_CH_EN   | 3F | Channels 1–6 are enabled.                                                                                 |

| 0x52 | SEQ_ON_LOG[3] | 01 | The rail on VIN3A is<br>up in the first SYNC<br>pulse record as first<br>sequence log.    | 0x1F | VRANGE_MULT | 30 | VIN1–VIN4 are 1x<br>scaling,<br>VIN5and VIN6 are 4x<br>scaling.                                           |

| 0x53 | SEQ_ON_LOG[4]   | 02 | The rail on VIN4A is<br>up in the second<br>SYNC pulse record as<br>second sequence log.        | 0xA1 | AMSK_ON       | 3F | AMSK_ON for VIN1–<br>VIN6 is enabled.                     |

|------|-----------------|----|-------------------------------------------------------------------------------------------------|------|---------------|----|-----------------------------------------------------------|

| 0x54 | SEQ_ON_LOG[5]   | 03 | The rail on VIN5A is<br>up in the third SYNC<br>pulse record as third<br>sequence log.          | 0xA2 | AMSK_OFF      | 3F | AMSK_OFF for VIN1-<br>VIN6 is enabled.                    |

| 0x55 | SEQ_ON_LOG[6]   | 02 | The rail on VIN6A is<br>up in the second<br>SYNC pulse record as<br>the second<br>sequence log. | 0xA3 | AMSK_EXS      | 06 | AMSK_EXS for VIN1,<br>VIN4, VIN5, and VIN6<br>is enabled. |

| 0x90 | SEQ_TIME_MSB[1] | 01 | The up time of VIN1A is 14.75ms.                                                                | 0xA4 | AMSK_ENS      | 06 | AMSK_ENS for VIN1,<br>VIN4, VIN5, and VIN6<br>is enabled. |

| 0x91 | SEQ_TIME_LSB[1] | 27 |                                                                                                 | 0xA5 | SEQ_TOUT_MSB  | 00 | The timeout set is to                                     |

| 0x92 | SEQ_TIME_MSB[2] | 01 | The up time of VIN2A                                                                            | 0xA6 | SEQ_TOUT_LSB  | 25 | 38ms.                                                     |

| 0x93 | SEQ_TIME_LSB[2] | DC | is 23.8ms.                                                                                      | 0xA7 | SEQ_SYNC      | C3 | PULSE_WIDTH is set to 2000µs.                             |

| 0x94 | SEQ_TIME_MSB[3] | 00 | The up time of VIN3A                                                                            | 0xA8 | SEQ_UP_THLD   | 3F | The UP rail threshold is the UV threshold.                |

| 0x95 | SEQ_TIME_LSB[3] | 1D | is 1.45ms.                                                                                      | 0xA9 | SEQ_DN_THLD   | 00 | The OFF rail threshold is the OFF threshold.              |

| 0x96 | SEQ_TIME_MSB[4] | 00 | The up time of VIN4A                                                                            | 0xB0 | SEQ_ON_EXP[1] | 03 | The expected<br>sequence log for<br>VIN1A is 3.           |

| 0x97 | SEQ_TIME_LSB[4] | 7B | is 6.15ms.                                                                                      | 0xB1 | SEQ_ON_EXP[2] | 04 | The expected<br>sequence log for<br>VIN2A is 4.           |

| 0x98 | SEQ_TIME_MSB[5] | 01 | The up time of VIN5A                                                                            | 0xB2 | SEQ_ON_EXP[3] | 01 | The expected<br>sequence log for<br>VIN3A is 1.           |

| 0x99 | SEQ_TIME_LSB[5] | 17 | is 13.95ms.                                                                                     | 0xB3 | SEQ_ON_EXP[4] | 02 | The expected<br>sequence log for<br>VIN4A is 2.           |

| 0x9A | SEQ_TIME_MSB[6] | 00 | The up time of VIN6A                                                                            | 0xB4 | SEQ_ON_EXP[5] | 03 | The expected<br>sequence log for<br>VIN5A is 3.           |

| 0x9B | SEQ_TIME_MSB[6] | 72 | is 5.7ms.                                                                                       | 0xB5 | SEQ_ON_EXP[6] | 02 | The expected<br>sequence log for<br>VIN6A is 2.           |

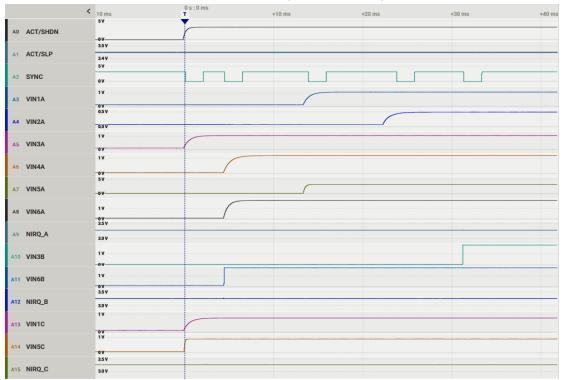

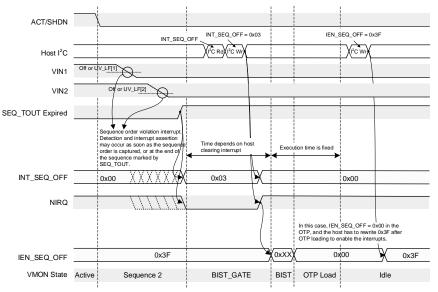

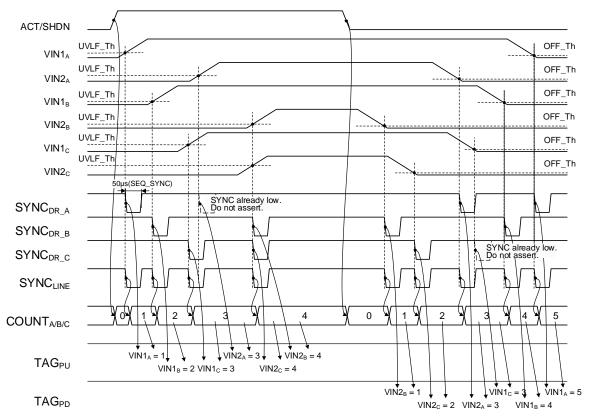

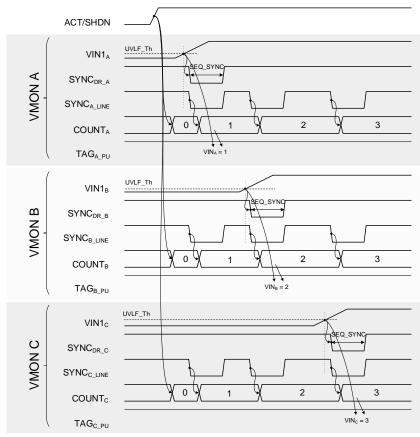

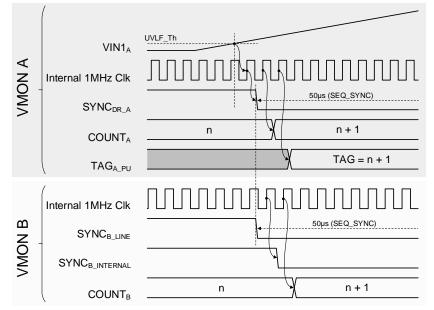

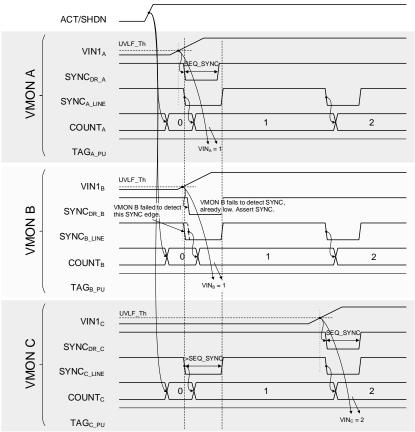

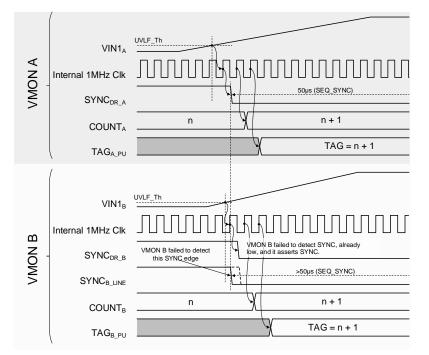

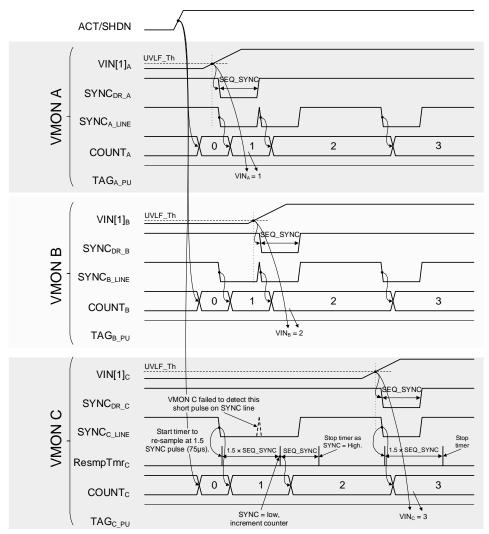

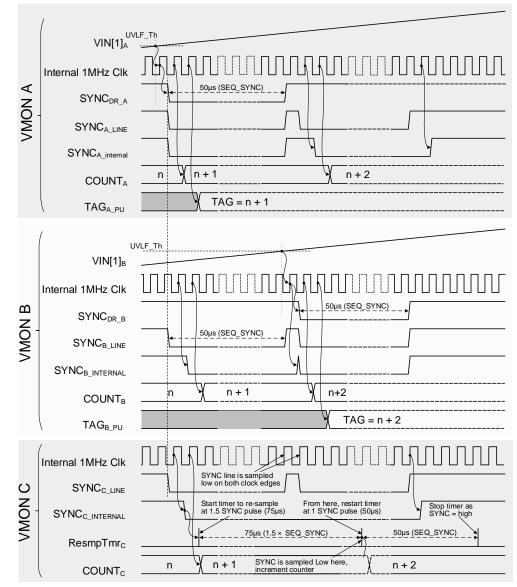

#### SEQ Monitoring On with Multiple MPQ79500FS Devices

Three MPQ79500FS devices, ACT/SHDN = low to high, ACT/SLP = high

#### Table 2: Read Register after Timeout

|                    |                                       |                | Part A                                                                                     |                | Part B                                               | Part C         |                                                                                            |  |

|--------------------|---------------------------------------|----------------|--------------------------------------------------------------------------------------------|----------------|------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------|--|

| Add.               | Register<br>Name                      | Read<br>Result | Description                                                                                | Read<br>Result | Description                                          | Read<br>Result | Description                                                                                |  |

|                    |                                       |                |                                                                                            | Bank (         | )                                                    |                |                                                                                            |  |

| 0x10<br>~10x<br>24 | Interrupt<br>Information<br>Registers | 00             | No interrupt after<br>SEQ_ON.                                                              | 00             | No interrupt after SEQ is on.                        | 00             | No interrupt after<br>SEQ_ON.                                                              |  |

| 0x32               | OFF_<br>STAT                          | 00             | Channels 1–6 are in the on state.                                                          | 1B             | Channel 3 and channel 6 are in the on state.         | 2E             | Channel 1 and channel 5 are in the on state.                                               |  |

| 0x36               | SEQ_<br>ORD_<br>STAT                  | 05             | 5 sync pulse count.                                                                        | 05             | 5 sync pulse count.                                  | 05             | 5 sync pulse count.                                                                        |  |

| 0x40               | VIN_<br>LVL[1]                        | AC             | VIN1A is 1.06V in the active state after SEQ_ON.                                           | 00             | VIN1B is not on.                                     | 78             | VIN1A is 0.8V at active state after SEQ_ON.                                                |  |

| 0x41               | VIN_<br>LVL[2]                        | 3D             | VIN2A is 0.505V in active<br>state after SEQ_ON.                                           | 00             | VIN2B is not on.                                     | 00             | VIN2C is not on.                                                                           |  |

| 0x42               | VIN_LVL[3]                            | AA             | VIN3A is 1.05V in the<br>active state after SEQ_ON.                                        | 32             | VIN3B is 1.8V at active state after SEQ is on.       | 00             | VIN3C is not on.                                                                           |  |

| 0x43               | VIN_LVL[4]                            | C8             | VIN4A is 1.2V in the active state after SEQ_ON.                                            | 00             | VIN4B is not on.                                     | 00             | VIN4C is not on.                                                                           |  |

| 0x44               | VIN_LVL[5]                            | 7B             | VIN5A is 3.26V in the active state after SEQ_ON.                                           | 00             | VIN5B is not on.                                     | 8C             | VIN5C is 0.9V at active state after SEQ_ON.                                                |  |

| 0x45               | VIN_LVL[6]                            | 32             | VIN6A is 1.8V in the active state after SEQ_ON.                                            | 32             | VIN6B is 1.8V at active state after SEQ_ON.          | 00             | VIN6C is not on.                                                                           |  |

| 0x50               | SEQ_ON_L<br>OG[1]                     | 03             | The rail on VIN1A is up in<br>the first SYNC pulse<br>record as the first<br>sequence log. | 00             | VIN1B does not have a<br>sequence when SEQ is<br>on. | 01             | The rail on VIN1C is up<br>in the first SYNC pulse<br>record as the first<br>sequence log. |  |

|      |                               |    |                                                                                              |    |                                                                                              |    | ГI                                                                                |

|------|-------------------------------|----|----------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------|

| 0x51 | SEQ_ON_<br>LOG[2]             | 04 | The rail on VIN2A is up<br>in the fourth SYNC pulse<br>record as the fourth<br>sequence log. | 00 | VIN2B does not have a sequence when SEQ is on.                                               | 00 | VIN2C does not have a sequence when SEQ is on.                                    |

| 0x52 | SEQ_ON_<br>LOG[3]             | 01 | The rail on VIN3A is up<br>in the first SYNC pulse<br>record as the first<br>sequence log.   | 05 | The rail on VIN3B is up in the fifth SYNC pulse record as the fifth sequence log.            | 00 | VIN3C does not have a sequence when SEQ is on.                                    |

| 0x53 | SEQ_ON_<br>LOG[4]             | 02 | The rail on VIN4A is up<br>in the second SYNC<br>pulse record as the<br>second sequence log. | 00 | VIN4B does not have a sequence when SEQ is on.                                               | 00 | VIN4C does not have a sequence when SEQ is on.                                    |

| 0x54 | SEQ_ON_<br>LOG[5]             | 03 | The rail on VIN5A is up<br>in the third SYNC pulse<br>record as the third<br>sequence log.   | 00 | VIN5B does not have a sequence when SEQ is on.                                               | 01 | The rail on VIN5C is up in the first SYNC pulse record as the first sequence log. |

| 0x55 | SEQ_ON_<br>LOG[6]             | 02 | The rail on VIN6A is up<br>in the second SYNC<br>pulse record as the<br>second sequence log. | 02 | The rail on VIN6B is up in<br>the second SYNC pulse<br>record as the second<br>sequence log. | 00 | VIN6C does not have a sequence when SEQ is on.                                    |

| 0x90 | SEQ_TIME_<br>MSB[1]           | 01 | The up time for VIN1A is                                                                     | 00 | VIN1B does not have a                                                                        | 00 | The up time of VIN1C is                                                           |

| 0x91 | SEQ_TIME_<br>LSB[1]           | 28 | 14.8ms.                                                                                      | 00 | sequence when SEQ is on.                                                                     | 1F | 1.55ms.                                                                           |

| 0x92 | SEQ_TIME_                     | 01 |                                                                                              | 00 |                                                                                              | 00 |                                                                                   |

| 0x93 | MSB[2]<br>SEQ_TIME_           | DD | The up time for VIN2A is 23.85ms.                                                            | 00 | VIN2B does not have a sequence when SEQ is on.                                               | 00 | VIN2C does not have a sequence when SEQ is on.                                    |

| 0x94 | LSB[2]<br>SEQ_TIME_           | 00 |                                                                                              | 02 |                                                                                              | 00 |                                                                                   |

| 0x95 | MSB[3]<br>SEQ_TIME_           | 1D | The up time for VIN3A is 1.45ms.                                                             | 71 | The up time of VIN3B is 31.25ms.                                                             | 00 | VIN3C does not have a sequence when SEQ is on.                                    |

| 0x96 | LSB[3]<br>SEQ_TIME_<br>MSB[4] | 00 | The up time for VIN4A is                                                                     | 00 | VIN4B does not have a                                                                        | 00 | VIN4C does not have a                                                             |

| 0x97 | SEQ_TIME_<br>LSB[4]           | 7B | 6.15ms.                                                                                      | 00 | sequence when SEQ is on.                                                                     | 00 | sequence when SEQ is on.                                                          |

| 0x98 | SEQ_TIME_<br>MSB[5]           | 01 | The up time for VIN5A is                                                                     | 00 | VIN5B does not have a                                                                        | 00 | The up time of VIN5C is                                                           |

| 0x99 | SEQ_TIME_<br>LSB[5]           | 17 | 13.95ms.                                                                                     | 00 | sequence when SEQ is on.                                                                     | 03 | 0.15ms.                                                                           |

| 0x9A | SEQ_TIME_<br>MSB[6]           | 00 | The up time for VIN6A is                                                                     | 00 | The up time of VIN6B is                                                                      | 00 | VIN6C does not have a                                                             |

| 0x9B | SEQ_TIME_<br>MSB[6]           | 72 | 5.7ms.                                                                                       | 5B | 4.55ms.                                                                                      | 00 | sequence when SEQ is on.                                                          |

|      | [0]                           |    |                                                                                              | E  | Bank 1                                                                                       |    | 1                                                                                 |

| 0x1E | VIN_CH_EN                     | 3F | Channels 1–6 are enabled.                                                                    | 24 | Channel 3 and channel 6 are enabled.                                                         | 11 | Channel 1 and channel 5 are all enabled.                                          |

| 0x1F | VRANGE_<br>MULT               | 30 | VIN1–VIN4 are 1x<br>scaling, VIN5 and VIN6<br>are 4x scaling.                                | 37 | VIN3 and VIN6 are 4x scaling.                                                                | 37 | VIN1 and VIN5 are 1x scaling.                                                     |

| 0xA1 | AMSK_ON                       | 3F | AMSK_ON for VIN1–<br>VIN6 is enabled.                                                        | 3C | AMSK_ON for VIN3 and VIN6 is enabled.                                                        | 3C | AMSK_ON for VIN1 and VIN5 is enabled.                                             |

| 0xA2 | AMSK_OFF                      | 3F | AMSK_OFF for VIN1–<br>VIN6 are all enabled.                                                  | 3C | AMSK_OFF for VIN3 and VIN6 is enabled.                                                       | 3C | AMSK_OFF for VIN1 and VIN5 is enabled.                                            |

| 0xA3 | AMSK_EXS                      | 06 | AMSK_EXS for VIN1,<br>VIN4, VIN5, and VIN6 is<br>enabled.                                    | 20 | AMSK_EXS for VIN6 is<br>enabled, AMSK_EXS of<br>VIN3 is disabled.                            | 20 | AMSK_EXS for VIN1 and VIN5 is enabled.                                            |

| 0xA4 | AMSK_ENS                      | 06 | AMSK_ENS for VIN1,<br>VIN4, VIN5, and VIN6<br>are enabled.                                   | 20 | AMSK_ENS for VIN6 is<br>enabled, AMSK_ENS of<br>VIN3 is disabled.                            | 20 | AMSK_ENS for VIN1 and VIN5 is enabled.                                            |

| 0xA5 | SEQ_TOUT<br>_MSB  | 00 | The timeout is set to 38ms.                  |    | The timeout is set to 38ms.                  | 00 | The timeout is set to 38ms.                  |

|------|-------------------|----|----------------------------------------------|----|----------------------------------------------|----|----------------------------------------------|

| 0xA6 | SEQ_TOUT<br>_LSB  | 25 | The lineout is set to soms.                  | 25 | The timeout is set to soms.                  | 25 | The timeout is set to soms.                  |

| 0xA7 | SEQ_SYNC          | C3 | PULSE_WIDTH is set to 2000µs.                | C3 | PULSE_WIDTH is set to 2000µs.                | C3 | PULSE_WIDTH is set to 2000µs.                |

| 0xA8 | SEQ_UP_<br>THLD   | 3F | The UP rail threshold is the UV threshold.   | 3F | The UP rail threshold is the UV threshold.   | 3F | The UP rail threshold is the UV threshold.   |

| 0xA9 | SEQ_DN_<br>THLD   | 00 | The OFF rail threshold is the OFF threshold. | 00 | The OFF rail threshold is the OFF threshold. | 00 | The OFF rail threshold is the OFF threshold. |

| 0xB0 | SEQ_ON_<br>EXP[1] | 03 | The expected sequence<br>log of VIN1A is 3.  | 00 | The expected sequence<br>log of VIN1B is 0.  | 01 | Expected sequence log of VIN1C is 1.         |

| 0xB1 | SEQ_ON_<br>EXP[2] | 04 | The expected sequence<br>log of VIN2A is 4.  | 00 | The expected sequence<br>log of VIN2B is 0.  | 00 | The expected sequence<br>log of VIN2C is 0.  |

| 0xB2 | SEQ_ON_<br>EXP[3] | 01 | The expected sequence<br>log of VIN3A is 1.  | 05 | The expected sequence<br>log of VIN3B is 5.  | 00 | The expected sequence<br>log of VIN3C is 0.  |

| 0xB3 | SEQ_ON_<br>EXP[4] | 02 | The expected sequence<br>log of VIN4A is 2.  | 00 | The expected sequence<br>log of VIN4B is 0.  | 00 | The expected sequence<br>log of VIN4C is 0.  |

| 0xB4 | SEQ_ON_<br>EXP[5] | 03 | The expected sequence log of VIN5A is 3.     | 00 | The expected sequence log of VIN5B is 0.     | 01 | The expected sequence log of VIN5C is 1.     |

| 0xB5 | SEQ_ON_<br>EXP[6] | 02 | The expected sequence log of VIN6A is 2.     | 02 | The expected sequence log of VIN6B is 2.     | 00 | The expected sequence log of VIN6C is 0.     |

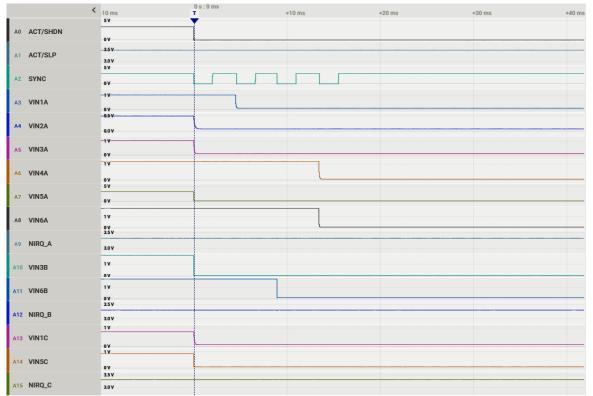

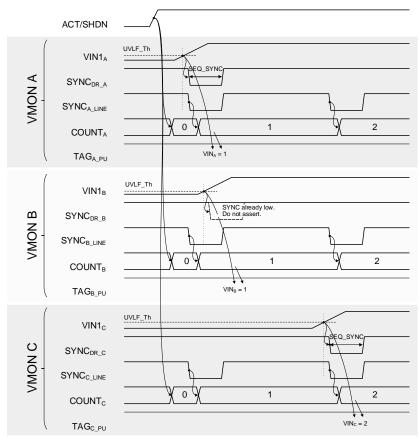

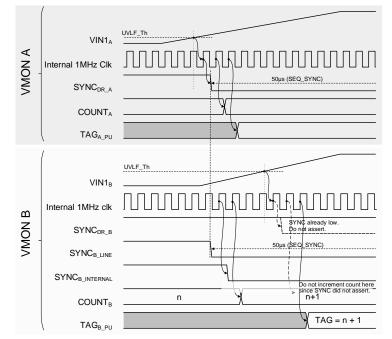

# **SEQ Monitoring Off with Multiple MPQ79500FS Devices** Three MPQ79500FS devices, ACT/SHDN = high to low, ACT/SLP = high

|               |                                       |                | Part A                                                                                            |                | Part B                                                                                       |                | Part C                                                                                       |

|---------------|---------------------------------------|----------------|---------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------|

| Add.          | Register<br>Name                      | Read<br>Result | Description                                                                                       | Read<br>Result | Description                                                                                  | Read<br>Result | Description                                                                                  |

|               | 1 .                                   |                | 1                                                                                                 | Ban            | k 0                                                                                          |                |                                                                                              |

| 0x10~<br>0x24 | Interrupt<br>Information<br>Registers | 00             | No interrupt after SEQ_OFF.                                                                       | 00             | No interrupt after SEQ_OFF.                                                                  | 00             | No interrupt after<br>SEQ_OFF.                                                               |

| 0x32          | OFF_STAT                              | 3F             | Channels 1–6 are in an off state.                                                                 | 3F             | Channel 3 and channel 6 are in an off state.                                                 | 2E             | Channel 1 and channel 5 are in an on state.                                                  |

| 0x36          | SEQ_ORD<br>_STAT                      | 04             | 4 sync pulse count.                                                                               | 04             | 4 sync pulse count.                                                                          | 04             | 4 sync pulse count.                                                                          |

| 0x40          | VIN_LVL[1]                            | 00             | VIN1A < 0.2V after<br>SEQ_OFF.                                                                    | 00             | VIN1B < 0.8V after<br>SEQ_OFF.                                                               | 00             | VIN1C < 0.2V after<br>SEQ_OFF.                                                               |

| 0x41          | VIN_LVL[2]                            | 00             | VIN2A < 0.2V after<br>SEQ_OFF.                                                                    | 00             | VIN2B < 0.8V after<br>SEQ_OFF.                                                               | 00             | VIN2C < 0.8V after<br>SEQ_OFF.                                                               |

| 0x42          | VIN_LVL[3]                            | 00             | VIN3A < 0.2V after<br>SEQ_OFF.                                                                    | 00             | VIN3B < 0.8V after<br>SEQ_OFF.                                                               | 00             | VIN3C < 0.8V after<br>SEQ_OFF.                                                               |

| 0x43          | VIN_LVL[4]                            | 00             | VIN4A < 0.2V after<br>SEQ_OFF.                                                                    | 00             | VIN4B < 0.2V after<br>SEQ_OFF.                                                               | 00             | VIN4C < 0.8V after<br>SEQ_OFF.                                                               |

| 0x44          | VIN_LVL[5]                            | 00             | VIN5A < 0.8V after<br>SEQ_OFF.                                                                    | 00             | VIN5B < 0.8V after<br>SEQ_OFF.                                                               | 00             | VIN5C < 0.2V after<br>SEQ_OFF.                                                               |

| 0x45          | VIN_LVL[6]                            | 00             | VIN6A < 0.8V after<br>SEQ_OFF.                                                                    | 00             | VIN6B < 0.8V after<br>SEQ_OFF.                                                               | 00             | VIN6C < 0.2V after<br>SEQ_OFF.                                                               |

| 0x60          | SEQ_OFF_<br>LOG[1]                    | 02             | The rail on VIN1A Is<br>down in the second<br>SYNC pulse record<br>as the first sequence<br>log.  | 00             | VIN1B does not have a sequence when SEQ is off.                                              | 01             | The rail on VIN1C is<br>down in the first SYNC<br>pulse record as the first<br>sequence log. |

| 0x61          | SEQ_OFF_<br>LOG[2]                    | 01             | The rail on VIN2A is<br>down in the first<br>SYNC pulse record<br>as the first sequence<br>log.   | 00             | VIN2B does not have a sequence when SEQ is off.                                              | 00             | VIN2C does not have a sequence when SEQ is off.                                              |

| 0x62          | SEQ_OFF_<br>LOG[3]                    | 01             | The rail on VIN3A is<br>down in the first<br>SYNC pulse record<br>as the first sequence<br>log.   | 01             | The rail on VIN3B is<br>down in the first SYNC<br>pulse record as the first<br>sequence log. | 00             | VIN3C does not have a sequence when SEQ is off.                                              |

| 0x63          | SEQ_OFF_<br>LOG[4]                    | 04             | The rail on VIN4A is<br>down in the fourth<br>SYNC pulse record<br>as the fourth<br>sequence log. | 00             | VIN4B does not have a sequence when SEQ is off.                                              | 00             | VIN4C does not have a sequence when SEQ is off.                                              |

| 0x64          | SEQ_OFF_<br>LOG[5]                    | 01             | The rail on VIN5A is<br>down in the first<br>SYNC pulse record<br>as the first sequence<br>log.   | 00             | VIN5B does not have a sequence when SEQ is off.                                              | 01             | The rail on VIN5C is<br>down in the first SYNC<br>pulse record as the first<br>sequence log. |

| 0x65          | SEQ_OFF_<br>LOG[6]                    | 04             | The rail on VIN6A Is<br>Down in the fourth<br>SYNC pulse record<br>as the fourth<br>sequence log. | 03             | The rail on VIN6B is<br>down in the third SYNC<br>pulse record as the third<br>sequence log. | 00             | VIN6C does not have a sequence when SEQ is off.                                              |

#### Table 3: Read Register after Timeout

| 0.00 | SEQ_TIME_           | 00 |                                                                  | 00  |                                                                    | 00 |                                              |

|------|---------------------|----|------------------------------------------------------------------|-----|--------------------------------------------------------------------|----|----------------------------------------------|

| 0x90 | MSB[1]              | 00 | The off time of                                                  | 00  | VIN1B does not have a sequence when SEQ is                         | 00 | The off time of VIN1C Is                     |

| 0x91 | SEQ_TIME_<br>LSB[1] | 5C | VIN1A is 4.6ms.                                                  | 00  | off.                                                               | 03 | 0.15ms.                                      |

| 0x92 | SEQ_TIME_<br>MSB[2] | 00 | The off time of                                                  | 00  | VIN2B does not have a                                              | 00 | VIN2C does not have a                        |

| 0x93 | SEQ_TIME_<br>LSB[2] | 03 | VIN2A is 0.15ms.                                                 | 00  | sequence when SEQ is off.                                          | 00 | sequence when SEQ is off.                    |

| 0x94 | SEQ_TIME_<br>MSB[3] | 00 | The off time of                                                  | 00  | The off time of VIN3B Is                                           | 00 | VIN3C does not have a                        |

| 0x95 | SEQ_TIME_<br>LSB[3] | 02 | VIN3A is 0.1ms.                                                  | 00  | 0ms.                                                               | 00 | sequence when SEQ is off.                    |

| 0x96 | SEQ_TIME_<br>MSB[4] | 01 | The off time of                                                  | 00  | VIN4B does not have a                                              | 00 | VIN4C does not have a                        |

| 0x97 | SEQ_TIME_<br>LSB[4] | 0E | VIN4A is 13.5ms.                                                 | 00  | sequence when SEQ is off.                                          | 00 | sequence when SEQ is off.                    |

| 0x98 | SEQ_TIME_<br>MSB[5] | 00 | The off time of                                                  | 00  | VIN5B does not have a                                              | 00 | The off time of VIN5C is                     |

| 0x99 | SEQ_TIME_<br>LSB[5] | 00 | VIN5A is 0ms.                                                    | 00  | sequence when SEQ is off.                                          | 00 | 0ms.                                         |

| 0x9A | SEQ_TIME_<br>MSB[6] | 01 | The off time of                                                  | 00  | The off time of VIN6B is                                           | 00 | VIN6C does not have a                        |

| 0x9B | SEQ_TIME_<br>MSB[6] | 0D | VIN6A is 13.45ms.                                                | B2  | 8.9ms.                                                             | 00 | sequence when SEQ is off.                    |

|      |                     |    |                                                                  | Ban | k 1                                                                |    |                                              |

| 0x1E | VIN_CH_EN           | 3F | Channels 1-6 are all enabled.                                    | 24  | Channel 3 and channel 6 are all enabled.                           | 11 | Channel 1 and channel 5 are all enabled.     |

| 0x1F | VRANGE_<br>MULT     | 30 | VIN1–VIN4 are 1x<br>scaling,<br>VIN5 and VIN6 are<br>4x scaling. | 37  | VIN3 and VIN6 are 4x scaling.                                      | 37 | VIN1 and VIN5 are 1x scaling.                |

| 0xA1 | AMSK_ON             | 3F | AMSK_ON for<br>VIN1–VIN6 is<br>enabled.                          | 3C  | AMSK_ON for VIN3 and VIN6 is enabled.                              | 3C | AMSK_ON for VIN1 and VIN5 is enabled.        |

| 0xA2 | AMSK_OFF            | 3F | AMSK_OFF for<br>VIN1–VIN6 is<br>enabled.                         | 3C  | AMSK_OFF for VIN3 and VIN6 is enabled.                             | 3C | AMSK_OFF for VIN1 and VIN5 is enabled.       |

| 0xA3 | AMSK_EXS            | 06 | AMSK_EXS for<br>VIN1, VIN4, VIN5,<br>and VIN6 is<br>enabled.     | 20  | AMSK_EXS for VIN6 is<br>enabled, AMSK_EXS<br>for VIN3 is disabled. | 20 | AMSK_EXS for VIN1 and VIN5 is enabled.       |

| 0xA4 | AMSK_ENS            | 06 | AMSK_EXS for<br>VIN1, VIN4, VIN5,<br>and VIN6 is<br>enabled.     | 20  | AMSK_ENS for VIN6 is<br>enabled, AMSK_ENS<br>for VIN3 is disabled. | 20 | AMSK_ENS for VIN1<br>and VIN5 is enabled.    |

| 0xA5 | SEQ_TOUT<br>MSB     | 00 | The timeout is set                                               | 00  | The timeout is set to                                              | 00 | The timeout is set to                        |

| 0xA6 | SEQ_TOUT<br>_LSB    | 25 | to 38ms.                                                         | 25  | 38ms.                                                              | 25 | 38ms.                                        |

| 0xA7 | SEQ_SYNC            | C3 | PULSE_WIDTH is set to 2000µs.                                    | C3  | PULSE_WIDTH is set to 2000µs.                                      | C3 | PULSE_WIDTH is set to 2000µs.                |

| 0xA8 | SEQ_UP_<br>THLD     | 3F | The UP rail<br>threshold is the UV<br>threshold.                 | 3F  | The UP rail threshold is the UV threshold.                         | 3F | The UP rail threshold is the UV threshold.   |

| 0xA9 | SEQ_DN_<br>THLD     | 00 | The OFF rail<br>threshold is the<br>OFF threshold.               | 00  | The OFF rail threshold is the OFF threshold.                       | 00 | The OFF rail threshold is the OFF threshold. |

| 0xC0 | SEQ_OFF<br>_EXP[1] | 02 | The expected sequence log of VIN1A is 2. | 00 | The expected sequence log of VIN1B is 0.    | 01 | The expected sequence log of VIN1C is 1. |

|------|--------------------|----|------------------------------------------|----|---------------------------------------------|----|------------------------------------------|

| 0xC1 | SEQ_OFF<br>_EXP[2] | 01 | The expected sequence log of VIN2A is 1. | 00 | The expected sequence log of VIN2B is 0.    | 00 | The expected sequence log of VIN2C is 0. |

| 0xC2 | SEQ_OFF<br>_EXP[3] | 01 | The expected sequence log of VIN3A is 1. | 01 | The expected sequence log of VIN3B is 1.    | 00 | The expected sequence log of VIN3C is 0. |

| 0xC3 | SEQ_OFF<br>_EXP[4] | 04 | The expected sequence log of VIN4A is 4. | 00 | The expected sequence<br>log of VIN4B is 0. | 00 | The expected sequence log of VIN4C is 0. |

| 0xC4 | SEQ_OFF<br>_EXP[5] | 01 | The expected sequence log of VIN5A is 1. | 00 | The expected log of<br>VIN5B is 0.          | 01 | The expected sequence log of VIN5C is 1. |

| 0xC5 | SEQ_OFF<br>_EXP[6] | 04 | The expected sequence log of VIN6A is 4. | 03 | The expected sequence log of VIN6B is 3.    | 00 | The expected sequence log of VIN6C is 0. |

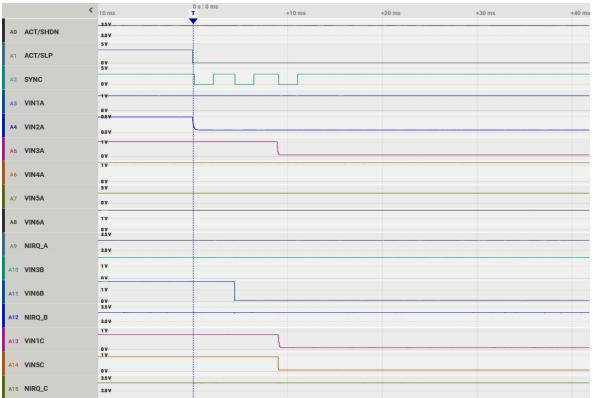

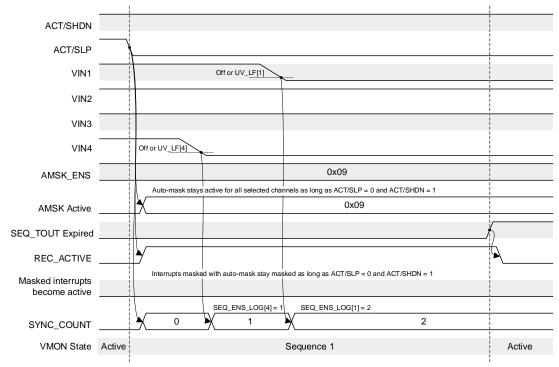

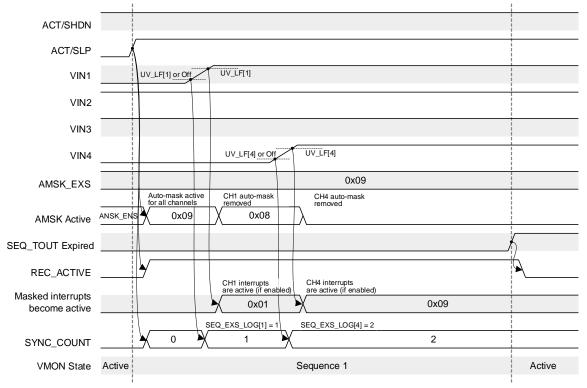

# SEQ Sleep Entry Monitoring with Multiple MPQ79500FS Devices Three MPQ79500FS devices, ACT/SHDN = high, ACT/SLP = high to low

|               | Part A                                |                |                                                                                                 | Part B         | Part C                                                                                            |                |                                                                                              |