# Dual Output Synchronous Buck PWM Controller

**ADP1877**

#### **FEATURES**

Input voltage range: 2.75 V to 14.5 V Output voltage range: 0.6 V to 90%  $V_{\rm IN}$

Maximum output current greater than 25 A per channel

Programmable frequency: 200 kHz to 1.5 MHz Flex-Mode architecture with integrated drivers

180° phase shift minimizes input ripple current and required input capacitance

$\pm 0.85\%$  output voltage accuracy  $-40^{\circ}$ C to  $+85^{\circ}$ C

**Integrated boost diodes**

Pulse skip high efficiency mode under light load

Power good with internal pull-up resistor

Overvoltage and overcurrent limit protection

Thermal overload protection

Input undervoltage lockout (UVLO)

Externally adjustable soft start, slope compensation and current sense gain

Independent precision enable inputs

**Synchronization input**

Suitable for any output capacitors

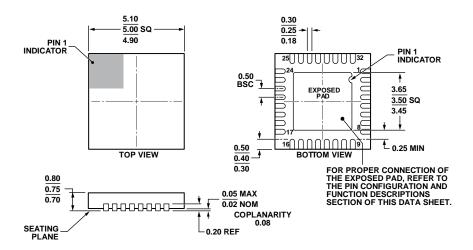

Available in 32-lead 5 mm × 5 mm LFCSP

#### **APPLICATIONS**

Set top boxes

**Printers**

**Communication infrastructure**

Distributor power dc systems

Industrial and instrumentation

#### **GENERAL DESCRIPTION**

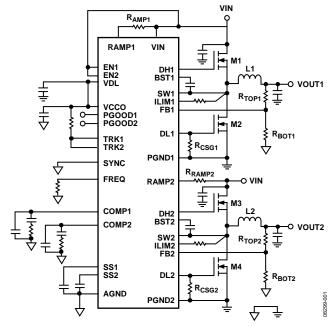

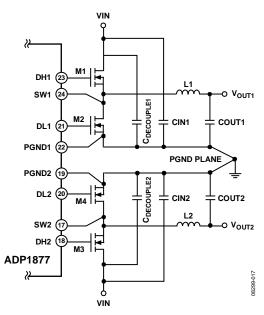

The ADP1877 is a Flex-Mode™ (proprietary architecture of Analog Devices, Inc.), dual-channel, step-down switching controller with integrated drivers that drive N-channel synchronous power MOSFETs. The two PWM outputs are phase shifted 180°, which reduces the input RMS current, thus minimizing required input capacitance.

The boost diodes are built into the ADP1877, thus lowering the overall system cost and component count. The ADP1877 can be set to operate in pulse skip high efficiency mode under light load or in PWM continuous conduction mode.

The ADP1877 includes externally adjustable soft start, output overvoltage protection, externally adjustable current limit, power good, and a programmable oscillator frequency that

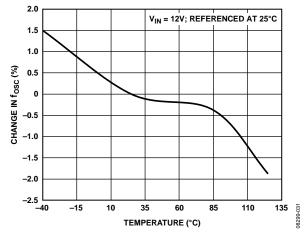

ranges from 200 kHz to 1.5 MHz. The ADP1877 provides an output voltage accuracy of  $\pm 0.85\%$  from  $-40^{\circ}$ C to  $+85^{\circ}$ C and  $\pm 1.5\%$  from  $-40^{\circ}$ C to  $125^{\circ}$ C in junction temperature. This part can be powered from a 2.75 V to 14.5 V supply, operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range, and is available in a 32-lead 5 mm  $\times$  5 mm LFCSP package.

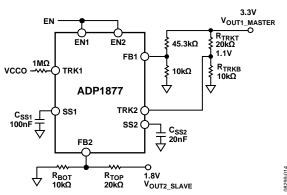

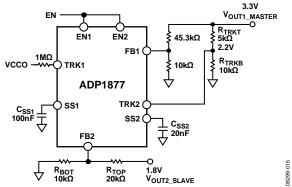

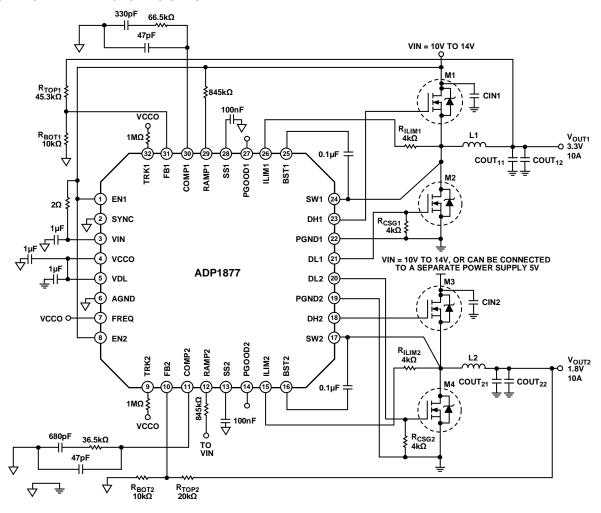

Figure 1. Typical Operation Circuit

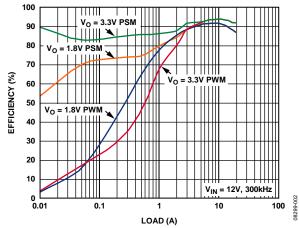

Figure 2. Efficiency Plot of Figure 42, 20 A Output

| TABLE OF CONTENTS                                           |                                                               |

|-------------------------------------------------------------|---------------------------------------------------------------|

| Features                                                    | Setting the Current Limit                                     |

| Applications1                                               | Accurate Current Limit Sensing17                              |

| General Description                                         | Setting the Slope Compensation                                |

| Revision History                                            | Setting the Current Sense Gain                                |

| Specifications                                              | Input Capacitor Selection19                                   |

| Absolute Maximum Ratings 6                                  | Input Filter19                                                |

| ESD Caution6                                                | Boost Capacitor Selection                                     |

| Simplified Block Diagram                                    | Inductor Selection                                            |

| Pin Configuration and Function Descriptions8                | Output Capacitor Selection                                    |

| Typical Performance Characteristics                         | MOSFET Selection21                                            |

| Theory of Operation                                         | Loop Compensation22                                           |

| Control Architecture                                        | Switching Noise and Overshoot Reduction                       |

| Oscillator Frequency13                                      | Voltage Tracking                                              |

| Mode of Operation14                                         | Coincident Tracking                                           |

| Synchronization14                                           | Ratiometric Tracking24                                        |

| Soft Start                                                  | PCB Layout Guideline                                          |

| Synchronous Rectifier and Dead Time15                       | MOSFETs, Input Bulk Capacitor, and Bypass Capacitor 25        |

| Input Undervoltage Lockout15                                | High Current and Current Sense Paths25                        |

| Internal Linear Regulator                                   | Signal Paths                                                  |

| Overvoltage Protection                                      | PGND Plane                                                    |

| Power Good15                                                | Feedback and Current Limit Sense Paths25                      |

| Short Circuit and Current Limit Protection16                | Switch Node                                                   |

| Shutdown Control16                                          | Gate Driver Paths                                             |

| Thermal Overload Protection16                               | Output Capacitors                                             |

| Applications Information                                    | Typical Operating Circuits                                    |

| Setting the Output Voltage                                  | Outline Dimensions                                            |

| Soft Start                                                  | Ordering Guide                                                |

| 2/                                                          |                                                               |

| REVISION HISTORY                                            |                                                               |

| 4/10—Rev. B to Rev. C                                       | 9/09—Rev. 0 to Rev. A                                         |

| Changes to Features and General Description                 | Changes to Features Section, General Description Section, and |

| Changes to Quiescent Current Parameter and FB to TRK Offset | Figure 21                                                     |

| Voltage Parameter, Table 1                                  | Changes to Output Characteristics, Feedback Accuracy Voltage  |

| Changes to Theory of Operation Section                      | Parameter; Error Amplifier, Transconductance Parameter; and   |

| Changes to Setting the Slope Compensation Section           | Linear Regulator, VCCO Load Regulation and VIN to VCCO        |

|                                                             | Dropout Voltage Parameters, Table 1                           |

| 11/09—Rev. A to Rev. B                                      | Changes to Pin 4, Pin 16, and Pin 25 Descriptions, Table 38   |

| Changes to Product Title                                    | Changes to Figure 5 and Figure 6                              |

| Changes to Signal Path Section                              | 0/00 P 11 0 T 11 1 7 1                                        |

|                                                             | 9/09—Revision 0: Initial Version                              |

# **SPECIFICATIONS**

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control.  $V_{IN}$  = 12 V. The specifications are valid for  $T_{J}$  =  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise specified. Typical values are at  $T_{A}$  =  $25^{\circ}$ C.

Table 1.

| Parameter                                | Symbol                          | Conditions                                                                                                                       | Min    | Тур    | Max    | Unit |

|------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------|

| POWER SUPPLY                             |                                 |                                                                                                                                  |        |        |        |      |

| Input Voltage                            | V <sub>IN</sub>                 |                                                                                                                                  | 2.75   |        | 14.5   | V    |

| Undervoltage Lockout Threshold           | IN <sub>UVLO</sub>              | V <sub>IN</sub> rising                                                                                                           | 2.45   | 2.6    | 2.75   | V    |

|                                          |                                 | V <sub>IN</sub> falling                                                                                                          | 2.4    | 2.5    | 2.6    |      |

| Undervoltage Lockout Hysteresis          |                                 |                                                                                                                                  |        | 0.1    |        | V    |

| Quiescent Current                        | I <sub>IN</sub>                 | $EN1 = EN2 = V_{IN} = 12 \text{ V}, V_{FB} = V_{CCO} \text{ in PWM mode}$ (no switching)                                         |        | 4.5    | 5.8    | mA   |

| Shutdown Current                         | I <sub>IN_SD</sub>              | $EN1 = EN2 = GND, V_{IN} = 5.5 \text{ V or } 14.5 \text{ V}$                                                                     |        | 100    | 200    | μΑ   |

| ERROR AMPLIFIER                          |                                 |                                                                                                                                  |        |        |        |      |

| FB Input Bias Current                    | I <sub>FB</sub>                 |                                                                                                                                  | -100   | +1     | +100   | nA   |

| Transconductance                         | G <sub>m</sub>                  | Sink or source 1 $\mu$ A, $T_A = 25$ °C                                                                                          | 440    | 550    | 660    | μS   |

|                                          |                                 | Sink or source 1 μA                                                                                                              | 385    | 550    | 715    | μS   |

| TRK1, TRK2 Input Bias Current            | I <sub>TRK</sub>                | 0 V < V <sub>TRK1/TRK2</sub> < 1.5 V                                                                                             | -100   | +1     | +100   | nA   |

| CURRENT SENSE AMPLIFIER GAIN             | Acs                             | Gain resistor connected to DL, $R_{CSG} = 47 \text{ k}\Omega \pm 5\%$                                                            | 2.4    | 3      | 3.6    | V/V  |

|                                          |                                 | Gain resistor connected to DL,<br>$R_{CSG} = 22 \text{ k}\Omega \pm 5\%$                                                         | 5.2    | 6      | 6.9    | V/V  |

|                                          |                                 | Default setting, R <sub>CSG</sub> = open                                                                                         | 10.5   | 12     | 13.5   | V/V  |

|                                          |                                 | Gain resistor connected to DL,<br>$R_{CSG} = 100 \text{ k}\Omega \pm 5\%$                                                        | 20.5   | 24     | 26.5   | V/V  |

| OUTPUT CHARACTERICTISTICS                |                                 |                                                                                                                                  |        |        |        |      |

| Feedback Accuracy Voltage                | $V_{FB}$                        | $T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}, V_{FB} = 0.6 \text{ V}$                                                      | -0.85% | +0.6   | +0.85% | V    |

|                                          |                                 | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}, V_{FB} = 0.6 \text{ V}$                                                     | -1.5%  | +0.6   | +1.5%  | V    |

| Line Regulation of PWM                   | $\Delta V_{FB}/\Delta V_{IN}$   | ·                                                                                                                                |        | ±0.015 |        | %/V  |

| Load Regulation of PWM                   | $\Delta V_{FB}/\Delta V_{COMP}$ | V <sub>COMP</sub> range 0.9 V to 2.2 V                                                                                           |        | ±0.3   |        | %    |

| OSCILLATOR                               |                                 | -                                                                                                                                |        |        |        |      |

| Frequency                                | f <sub>OSC</sub>                | $R_{FREQ} = 340 \text{ k}\Omega$ to AGND                                                                                         | 170    | 200    | 235    | kHz  |

|                                          |                                 | $R_{FREQ} = 78.7 \text{ k}\Omega \text{ to AGND}$                                                                                | 744    | 800    | 856    | kHz  |

|                                          |                                 | $R_{FREQ} = 39.2 \text{ k}\Omega \text{ to AGND}$                                                                                | 1275   | 1500   | 1725   | kHz  |

|                                          |                                 | FREQ to AGND                                                                                                                     | 235    | 300    | 345    | kHz  |

|                                          |                                 | FREQ to VCCO                                                                                                                     | 475    | 600    | 690    | kHz  |

| SYNC Input Frequency Range               | <b>f</b> <sub>SYNC</sub>        | $f_{SYNC} = 2 \times f_{sw}$ ; $f_{SYNC} = f_{OSC}$ ; the minimum sync frequency is $1 \times$ the $f_{OSC}$ set by the resistor | 400    |        | 3000   | kHz  |

| SYNC Input Pulse Width                   | t <sub>SYNCMIN</sub>            |                                                                                                                                  | 100    |        |        | ns   |

| SYNC Pin Capacitance to GND              | C <sub>SYNC</sub>               |                                                                                                                                  |        | 5      |        | рF   |

| LINEAR REGULATOR                         |                                 |                                                                                                                                  |        |        |        |      |

| VCCO Output Voltage                      |                                 | T <sub>A</sub> = 25°C, I <sub>VCCO</sub> = 100 mA                                                                                | 4.8    | 5.0    | 5.18   | ٧    |

|                                          |                                 | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                           | 4.7    | 5.0    | 5.3    | ٧    |

| VCCO Load Regulation                     |                                 | $I_{VCCO} = 0$ mA to 100 mA,                                                                                                     |        | 35     |        | mV   |

| VCCO Line Regulation                     |                                 | $V_{IN} = 5.5 \text{ V to } 14.5 \text{ V, } I_{VCCO} = 20 \text{ mA}$                                                           |        | 10     |        | mV   |

| VCCO Current Limit <sup>1</sup>          |                                 | VCCO drops to 4 V from 5 V                                                                                                       |        | 350    |        | mA   |

| VCCO Short-Circuit Current <sup>1</sup>  |                                 | VCCO < 0.5 V                                                                                                                     |        | 370    | 400    | mA   |

| VIN to VCCO Dropout Voltage <sup>2</sup> | V <sub>DROPOUT</sub>            | $I_{VCCO} = 100 \text{ mA}, V_{IN} \le 5 \text{ V}$                                                                              |        | 0.33   |        | V    |

| Parameter                                                          | Symbol                  | Conditions                                               | Min  | Тур  | Max     | Unit |

|--------------------------------------------------------------------|-------------------------|----------------------------------------------------------|------|------|---------|------|

| LOGIC INPUTS                                                       |                         |                                                          |      |      |         |      |

| EN1, EN2                                                           |                         | EN1/EN2 rising                                           | 0.57 | 0.63 | 0.68    | V    |

| EN1, EN2 Hysteresis                                                |                         |                                                          |      | 0.03 |         | V    |

| EN1, EN2 Input Leakage Current                                     | I <sub>EN</sub>         | $V_{IN} = 2.75 \text{ V to } 14.5 \text{ V}$             |      | 1    | 200     | nA   |

| SYNC Logic Input Low                                               |                         |                                                          |      |      | 1.3     | V    |

| SYNC Logic Input High                                              |                         |                                                          | 1.9  |      |         | V    |

| SYNC Input Leakage Current                                         | I <sub>SYNC</sub>       | SYNC = 5 V, internal 1 MΩ pull-down                      |      | 5    | 6.5     | μΑ   |

| GATE DRIVERS                                                       |                         |                                                          |      |      |         |      |

| DH Rise Time                                                       |                         | $C_{DH} = 3 \text{ nF, } V_{BST} - V_{SW} = 5 \text{ V}$ |      | 16   |         | ns   |

| DH Fall Time                                                       |                         | $C_{DH} = 3 \text{ nF, } V_{BST} - V_{SW} = 5 \text{ V}$ |      | 14   |         | ns   |

| DL Rise Time                                                       |                         | $C_{DL} = 3 \text{ nF}$                                  |      | 16   |         | ns   |

| DL Fall Time                                                       |                         | $C_{DL} = 3 \text{ nF}$                                  |      | 14   |         | ns   |

| DH to DL Dead Time                                                 |                         | External 3 nF is connected to DH and DL                  |      | 25   |         | ns   |

| DH or DL Driver R <sub>ON</sub> , Sourcing<br>Current <sup>1</sup> | Ron_sourc               | Sourcing 2 A with a 100 ns pulse                         |      | 2    |         | Ω    |

|                                                                    |                         | Sourcing 1 A with a 100 ns pulse, V <sub>IN</sub> = 3 V  |      | 2.3  |         | Ω    |

| DH or DL Driver R <sub>ON</sub> , Tempco                           | TC <sub>RON</sub>       | V <sub>IN</sub> = 3 V or 12 V                            |      | 0.3  |         | %/°C |

| DH or DL Driver R <sub>ON</sub> , Sinking<br>Current <sup>1</sup>  | Ron_sink                | Sinking 2 A with a 100 ns pulse                          |      | 1.5  |         | Ω    |

|                                                                    |                         | Sinking 1 A with a 100 ns pulse, $V_{IN} = 3 \text{ V}$  |      | 2    |         | Ω    |

| DH Maximum Duty Cycle                                              |                         | fosc = 300 kHz                                           | 90   |      |         | %    |

| DH Maximum Duty Cycle                                              |                         | f <sub>osc</sub> = 1500 kHz                              | 50   |      |         | %    |

| Minimum DH On Time                                                 |                         | fosc = 200 kHz to 1500 kHz                               |      |      | 130     | ns   |

| Minimum DH Off Time                                                |                         | $f_{OSC} = 200 \text{ kHz to } 1500 \text{ kHz}$         |      |      | 330     | ns   |

| Minimum DL On Time                                                 |                         | fosc = 200 kHz to 1500 kHz                               |      |      | 280     | ns   |

| COMP VOLTAGE RANGE                                                 |                         |                                                          |      |      |         |      |

| COMP Pulse Skip Threshold                                          | V <sub>COMP,THRES</sub> | In pulse skip mode                                       |      | 0.9  |         | V    |

| COMP Clamp High Voltage                                            | V <sub>COMP,HIGH</sub>  |                                                          | 2.25 |      |         | V    |

| THERMAL SHUTDOWN                                                   |                         |                                                          |      |      |         |      |

| Thermal Shutdown Threshold                                         | T <sub>TMSD</sub>       |                                                          |      | 155  |         | °C   |

| Thermal Shutdown Hysteresis                                        |                         |                                                          |      | 20   |         | °C   |

| OVERVOLTAGE AND POWER GOOD THRESHOLDS                              |                         |                                                          |      |      |         |      |

| FB Overvoltage Threshold                                           | Vov                     | V <sub>FB</sub> rising                                   | 0.67 | 0.7  | 0.73    | V    |

| FB Overvoltage Hysteresis                                          |                         | 1,5.1.5.1.9                                              |      | 40   |         | mV   |

| FB Undervoltage Threshold                                          | Vuv                     | V <sub>FB</sub> rising                                   | 0.51 | 0.54 | 0.57    | V    |

| FB Undervoltage Hysteresis                                         | 100                     |                                                          |      | 30   |         | mV   |

| TRK INPUT VOLTAGE RANGE                                            |                         |                                                          | 0    |      | 5       | V    |

| FB TO TRK OFFSET VOLTAGE                                           |                         | TRK = 0.5 V to 0.6 V; offset = $V_{FB} - V_{TRK}$        | -120 | -70  | <u></u> | mV   |

| SOFT START                                                         |                         | THE - 0.5 V CO 0.0 V, OHISCE - VID VIRA                  | 120  | ,,   |         | 1117 |

| SS Output Current                                                  | Iss                     | During start-up                                          | 4.6  | 6.5  | 8.4     | μΑ   |

| SS Pull-Down Resistor                                              | 133                     | During start-up  During a fault condition                | 7.0  | 1    | 0.4     | kΩ   |

| 33 i dil-DOWII NESISTOI                                            | 1                       | Daning a laun condition                                  |      |      |         | 1/77 |

| Parameter                                           | Symbol             | Conditions                                                          | Min | Тур  | Max | Unit |

|-----------------------------------------------------|--------------------|---------------------------------------------------------------------|-----|------|-----|------|

| PGOOD                                               |                    |                                                                     |     |      |     |      |

| PGOOD Pull-up Resistor                              | R <sub>PGOOD</sub> | Internal pull-up resistor to VCCO                                   |     | 12.5 |     | kΩ   |

| PGOOD Delay                                         |                    |                                                                     |     | 12   |     | μs   |

| Overvoltage or Undervoltage                         |                    | This is the minimum duration required to trip the PGOOD signal.     |     | 12   |     | μs   |

| Minimum Duration                                    |                    |                                                                     |     |      |     |      |

| ILIM1, ILIM2 Threshold Voltage <sup>1</sup>         |                    | Relative to PGND                                                    | -5  | 0    | +5  | mV   |

| ILIM1, ILIM2 Output Current                         |                    | ILIM = PGND                                                         | 40  | 50   | 60  | μΑ   |

| Current Sense Blanking Period                       |                    | After DL goes high, current limit is not sensed during this period. |     | 100  |     | ns   |

| INTEGRATED RECTIFIER<br>(BOOST DIODE) RESISTANCE    |                    | At 20 mA forward current                                            |     | 16   |     | Ω    |

| ZERO CURRENT CROSS OFFSET (SW TO PGND) <sup>1</sup> |                    | In pulse skip mode only; fosc = 600 kHz                             | 0   | 2    | 4   | mV   |

$<sup>^{1}</sup>$  Guaranteed by design.  $^{2}$  Connect V<sub>IN</sub> to VCCO when V<sub>IN</sub> < 5.5 V. For applications with V<sub>IN</sub> < 5.5 V and V<sub>IN</sub> not connected to VCCO, keep in mind that VCCO = V<sub>IN</sub> − VDROPOUT. VCCO must be ≥ 2.75 V for proper operation.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 1 duic 2.                                                                |                     |

|--------------------------------------------------------------------------|---------------------|

| Parameter                                                                | Rating              |

| VIN, EN1/EN2, RAMP1/RAMP2                                                | 15 V                |

| FB1/FB2, COMP1/COMP2, SS1/SS2,                                           | -0.3  V to  +6  V   |

| TRK1/TRK2, FREQ, SYNC, VCCO, VDL,                                        |                     |

| PGOOD1/PGOOD2                                                            |                     |

| ILIM1/ILIM2                                                              | -0.3  V to  +16  V  |

| BST1/BST2, DH1/DH2, SW1/SW2 to                                           | -0.3  V to  +22  V  |

| PGND1/PGND2                                                              |                     |

| DL1/DL2 to PGND1/PGND2                                                   | -0.3 V to VCCO +    |

|                                                                          | 0.3 V               |

| BST1/BST2 to PGND1/PGND2, SW1/SW2 to                                     | +25 V               |

| PGND1/PGND2 20 ns Transients                                             |                     |

| DL1/DL2, SW1/SW2, ILIM1/ILIM2 to                                         | –8 V                |

| PGND1/PGND2 20 ns Negative Transients                                    |                     |

| PGND1/PGND2 to AGND                                                      | -0.3  V to  +0.3  V |

| PGND1/PGND2 to AGND 20 ns Transients                                     | -8 V to +4 V        |

| $\theta_{JA}$ , =on a Multilayer PCB (Natural Convection) <sup>1,2</sup> | 32.6°C/W            |

| Operating Ambient Temperature Range <sup>3</sup>                         | -40°C to +85°C      |

| Operating Junction Temperature Range <sup>3</sup>                        | -40°C to +125°C     |

| Storage Temperature Range                                                | −65°C to +150°C     |

| Maximum Soldering Lead Temperature                                       | 260°C               |

<sup>1</sup> Measured with exposed pad attached to PCB.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified all other voltages are referenced to GND.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) of the package was calculated or simulated on a multilayer PCB.

<sup>&</sup>lt;sup>3</sup>The device can be damaged when the junction temperature limits are exceeded. Monitoring ambient temperature does not guarantee that  $T_J$  is within the specified temperature limits. In applications with moderate power dissipation and low PCB thermal resistance, the maximum ambient temperature can exceed the maximum limit as long as the junction temperature is within specification limits. The junction temperature,  $T_A$ , of the device is dependent on the ambient temperature,  $T_A$ , the power dissipation of the device,  $P_D$ , and the junction to ambient thermal resistance of the package,  $\theta_{JA}$ . Maximum junction temperature is calculated from the ambient temperature and power dissipation using the formula  $T_J = T_A + P_D \times \theta_{JA}$ .

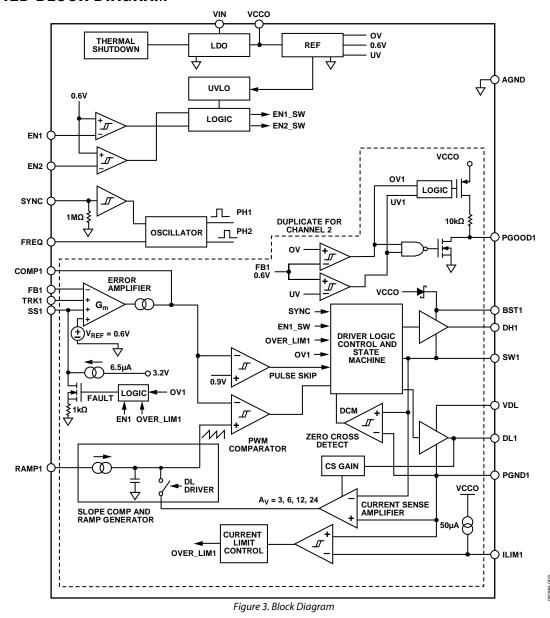

# SIMPLIFIED BLOCK DIAGRAM

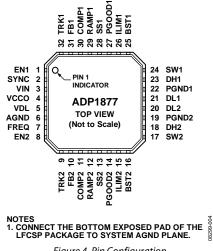

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN1      | Enable Input for Channel 1. Drive EN1 high to turn on the Channel 1 controller, and drive it low to turn off. Tie EN1 to VIN for automatic startup. For a precision UVLO, put an appropriately sized resistor divider from VIN to AGND, and tie the midpoint to this pin.                                                                                                                                                     |

| 2       | SYNC     | Frequency Synchronization Input. Accepts an external signal between $1 \times$ and $2.3 \times$ of the internal oscillator frequency, $f_{OSC}$ , set by the FREQ pin. The controller operates in forced PWM when a signal is detected at SYNC or when SYNC is high. The resulting switching frequency is $\frac{1}{2}$ of the SYNC frequency. When SYNC is low or left floating, the controller operates in pulse skip mode. |

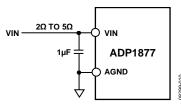

| 3       | VIN      | Connect to Main Power Supply. Bypass with a 1 $\mu$ F or larger ceramic capacitor connected as close to this pin as possible and PGND.                                                                                                                                                                                                                                                                                        |

| 4       | VCCO     | Output of the Internal Low Dropout Regulator (LDO). The internal circuitry and gate drivers are powered from VCCO. Bypass VCCO to AGND with a 1 µF or larger ceramic capacitor. The VCCO output is always active, even during fault conditions and cannot be turned off even if EN1/EN2 is low. For operations at VIN below 5 V, VIN can be jumped to VCCO. Do not use the LDO to power other auxiliary system loads.         |

| 5       | VDL      | Power Supply for the Low-Side Driver. Bypass VDL to PGND with a 1 $\mu$ F or greater ceramic capacitor. Connect VCCO to VDL.                                                                                                                                                                                                                                                                                                  |

| 6       | AGND     | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7       | FREQ     | Sets the desired operating frequency between 200 kHz and 1.5 MHz with one resistor between FREQ and AGND. See Table 4 for more details. Connect FREQ to AGND for a preprogrammed 300 kHz or FREQ to VCCO for a 600 kHz operating frequency.                                                                                                                                                                                   |

| 8       | EN2      | Enable Input for Channel 2. Drive EN2 high to turn on the Channel 2 controller, and drive it low to turn off. Tie EN2 to VIN for automatic startup. For a precision UVLO, put an appropriately sized resistor divider from VIN to AGND, and tie the midpoint to this pin.                                                                                                                                                     |

| 9       | TRK2     | Tracking Input for Channel 2. If the tracking function is not used, it is recommended to connect TRK2 to VCCO through a resistor higher than 1 M $\Omega$ , or simply connect TRK2 between 0.7 V and 2 V to reduce the bias current going into the TRK2 pin.                                                                                                                                                                  |

| 10      | FB2      | Output Voltage Feedback for Channel 2. Connect to Channel 2 via a resistor divider.                                                                                                                                                                                                                                                                                                                                           |

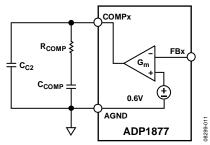

| 11      | COMP2    | Compensation Node for Channel 2. Output of Channel 2 error amplifier. Connect a series resistor-capacitor network from COMP2 to AGND to compensate the regulation control loop.                                                                                                                                                                                                                                               |

| 12      | RAMP2    | Programmable Current Setting for Slope Compensation of Channel 2. Connect a resistor from RAMP2 to VIN. The voltage at RAMP2 is 0.2 V.                                                                                                                                                                                                                                                                                        |

| 13      | SS2      | Soft Start Input for Channel 2. Connect a capacitor from SS2 to AGND to set the soft start period. This node is internally pulled up to 3.2 V through a 6.5 $\mu$ A current source.                                                                                                                                                                                                                                           |

| Pin No. | Mnemonic              | Description                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|---------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 14      | PGOOD2                | Open-drain power-good indicator logic output with an internal $12  k\Omega$ resistor connected between PGOOD2 and VCCO. PGOOD2 is pulled to ground when the Channel 2 output is outside the regulation window. An external pull-up resistor is not required.                    |  |  |  |  |  |  |

| 15      | ILIM2                 | Current Limit Sense Comparator Inverting Input for Channel 2. Connect a resistor between ILIM2 and SW2 to set the current limit offset. For accurate current limit sensing, connect ILIM2 to a current sense resistor at the source of the low-side MOSFET.                     |  |  |  |  |  |  |

| 16      | BST2                  | Boot Strapped Upper Rail of High Side Internal Driver for Channel 2. Connect a 0.1 µF to a 0.22 µF multilayer ceramic capacitor (MLCC) between BST2 and SW2. There is an internal boost rectifier connected between VCCO and BST2.                                              |  |  |  |  |  |  |

| 17      | SW2                   | Switch Node for Channel 2. Connect to the source of the high-side N-channel MOSFET and the drain of the low-side N-channel MOSFET of Channel 2.                                                                                                                                 |  |  |  |  |  |  |

| 18      | DH2                   | High-Side Switch Gate Driver Output for Channel 2. Capable of driving MOSFETs with total input capacitance up to 20 nF.                                                                                                                                                         |  |  |  |  |  |  |

| 19      | PGND2                 | Power Ground for Channel 2. Ground for internal Channel 2 driver. Differential current is sensed between SW2 and PGND2. It is not recommended to short PGND2 to PGND1 directly.                                                                                                 |  |  |  |  |  |  |

| 20      | DL2                   | Low-Side Synchronous Rectifier Gate Driver Output for Channel 2. To set the gain of the current sense amplifier, connect a resistor between DL2 and PGND2. Capable of driving MOSFETs with a total input capacitance up to 20 nF.                                               |  |  |  |  |  |  |

| 21      | DL1                   | Low-Side Synchronous Rectifier Gate Driver Output for Channel 1. To set the gain of the current sense amplifier, connect a resistor between DL1 and PGND1. Capable of driving MOSFETs with a total input capacitance up to 20 nF.                                               |  |  |  |  |  |  |

| 22      | PGND1                 | Power Ground for Channel 1. Ground for internal Channel 1 driver. Differential current is sensed between SW1 and PGND1. It is not recommended to short PGND2 to PGND1 directly.                                                                                                 |  |  |  |  |  |  |

| 23      | DH1                   | High-Side Switch Gate Driver Output for Channel 1. Capable of driving MOSFETs with a total input capacitance up to 20 nF.                                                                                                                                                       |  |  |  |  |  |  |

| 24      | SW1                   | Power Switch Node for Channel 1. Connect to the source of the high-side N-channel MOSFET and the drain of the low-side N-channel MOSFET of Channel 1.                                                                                                                           |  |  |  |  |  |  |

| 25      | BST1                  | Boot Strapped Upper Rail of High Side Internal Driver for Channel 1. Connect a 0.1 µF to a 0.22 µF multilayer ceramic capacitor (MLCC) between BST1 and SW1. There is an internal boost diode or rectifier connected between VCCO and BST1.                                     |  |  |  |  |  |  |

| 26      | ILIM1                 | Current Limit Sense Comparator Inverting Input for Channel 1. Connect a resistor between ILIM1 and SW1 to set the current limit offset. For accurate current limit sensing, connect ILIM1 to a current sense resistor at the source of the low-side MOSFET.                     |  |  |  |  |  |  |

| 27      | PGOOD1                | Power Good. Open drain power good indicator logic output with an internal $12 \text{ k}\Omega$ resistor connected between PGOOD1 and VCCO. PGOOD1 is pulled to ground when the Channel 1 output is outside the regulation window. An external pull-up resistor is not required. |  |  |  |  |  |  |

| 28      | SS1                   | Soft Start Input for Channel 1. Connect a capacitor from SS1 to AGND to set the soft start period. This node is internally pulled up to 3.2 V through a 6.5 µA current source.                                                                                                  |  |  |  |  |  |  |

| 29      | RAMP1                 | Programmable Current Setting for Slope Compensation of Channel 1. Connect a resistor from RAMP1 to VIN. The voltage at RAMP1 is 0.2 V during operation. This pin is high impedance when the channel is disabled.                                                                |  |  |  |  |  |  |

| 30      | COMP1                 | Compensation Node for Channel 1. Output of Channel 1 error amplifier. Connect a series resistor-capacitor network from COMP1 to AGND to compensate the regulation control loop.                                                                                                 |  |  |  |  |  |  |

| 31      | FB1                   | Output Voltage Feedback for Channel 1. Connect to Channel 1 via a resistor divider.                                                                                                                                                                                             |  |  |  |  |  |  |

| 32      | TRK1                  | Tracking Input for Channel 1. If the tracking function is not used, it is recommended to connect TRK1 to VCCO through a resistor higher than 1 M $\Omega$ , or simply connect TRK1 between 0.7 V and 2 V to reduce the bias current going into the TRK1 pin.                    |  |  |  |  |  |  |

| 33      | Bottom<br>exposed pad | Connect the bottom exposed pad of the LFCSP package to the system AGND plane.                                                                                                                                                                                                   |  |  |  |  |  |  |

# TYPICAL PERFORMANCE CHARACTERISTICS

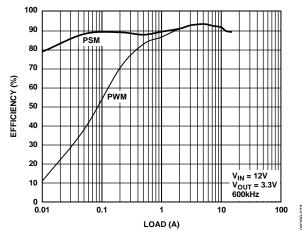

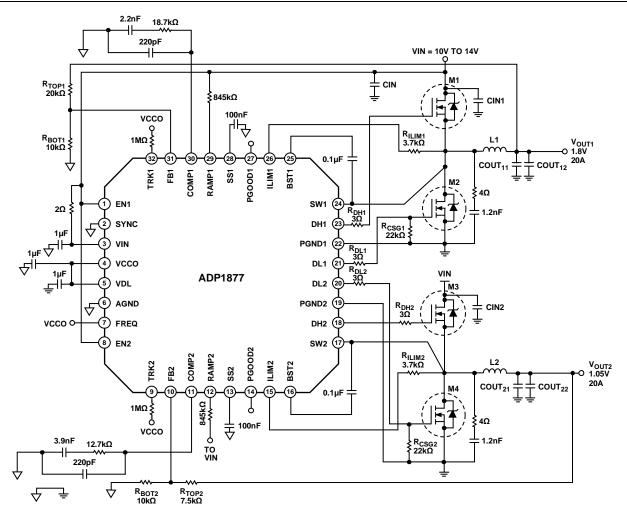

Figure 5. Efficiency Plot of Figure 41, 10 A Output

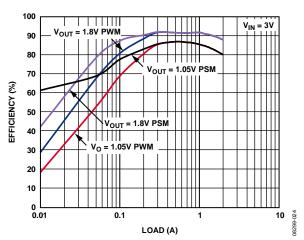

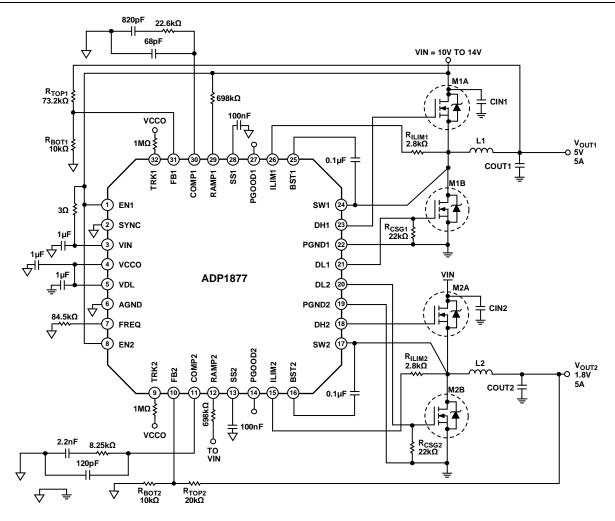

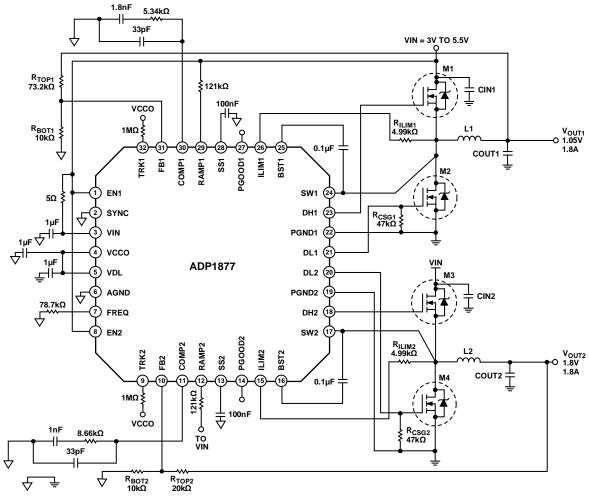

Figure 6. Efficiency Plot of Figure 44, 2 A Output

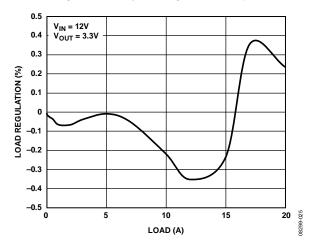

Figure 7. Load Regulation of Figure 42

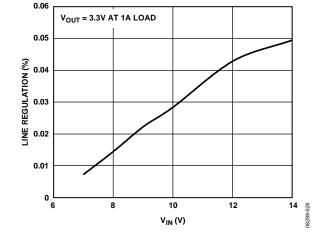

Figure 8. Line Regulation of Figure 42

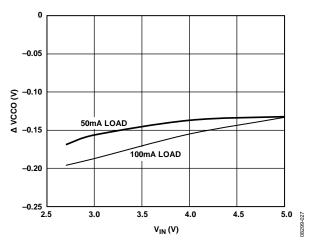

Figure 9. LDO Load Regulation

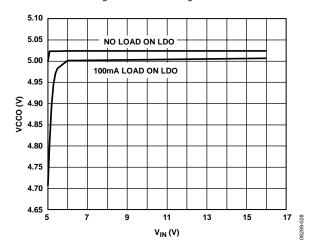

Figure 10. LDO Line Regulation

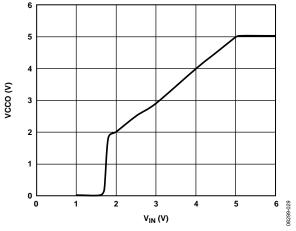

Figure 11. VCCO vs. V<sub>IN</sub>

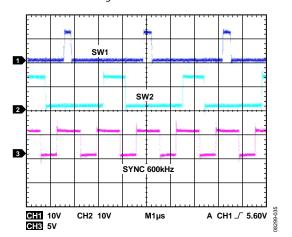

Figure 12. An Example of Synchronization,  $f_{SW} = 600 \text{ kHz}$

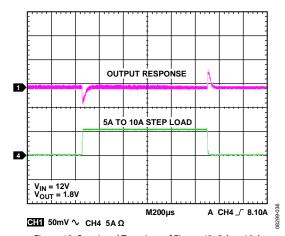

Figure 13. Step Load Transient of Figure 42, 5 A to 10 A

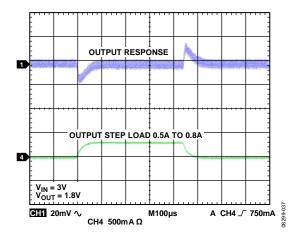

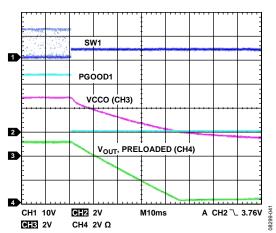

Figure 14. Step Load Transient of Figure 44

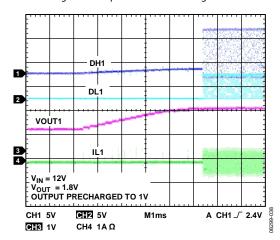

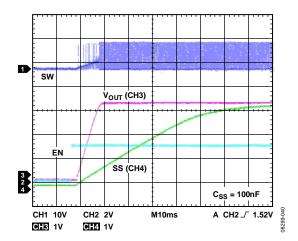

Figure 15. Soft Start into Precharged Output

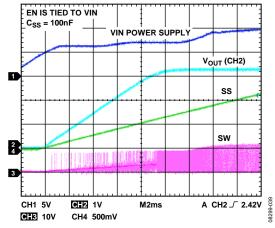

Figure 16. Power-On Sequence

Figure 17. Enable Function

Figure 18. Thermal Shutdown Waveform

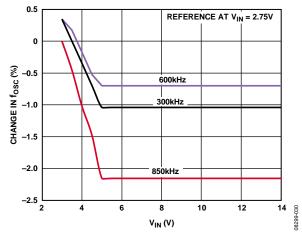

Figure 19. Change in fosc vs. V<sub>IN</sub>

Figure 20. f<sub>OSC</sub> vs. Temperature

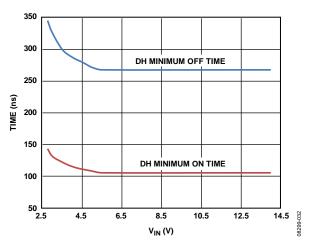

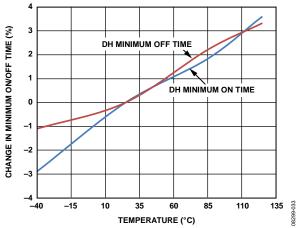

Figure 21. Typical DH Minimum On Time and Off Time

Figure 22. DH Minimum On Time and Off Time Overtemperature

### THEORY OF OPERATION

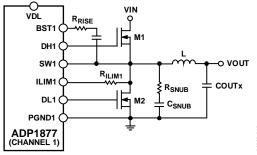

The ADP1877 is a current mode (using ADI proprietary Flex-Mode architecture), dual-channel, step-down switching controller with integrated MOSFET drivers that drive N-channel synchronous power MOSFETs. The two outputs are phase shifted 180°. This reduces the input RMS current, thus minimizing required input capacitance.

The ADP1877 can be set to operate in pulse skip high efficiency mode under light load or in forced PWM. The integrated boost diodes in the ADP1877 reduce the overall system cost and component count. The ADP1877 includes programmable soft start, output overvoltage protection, programmable current limit, power good, and tracking function. The ADP1877 can be set to operate in any switching frequency between 200 kHz and 1.5 MHz with one external resistor.

#### **CONTROL ARCHITECTURE**

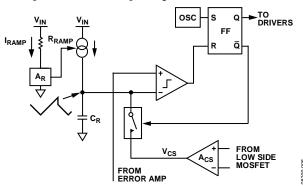

The ADP1877 is based on a fixed frequency current mode PWM control architecture. The inductor current is sensed by the voltage drop measured across the external low-side MOSFET R<sub>DSON</sub> during the off period of the switching cycle (valley inductor current). The current sense signal is further processed by the current sense amplifier. The output of the current sense amplifier is held, and the emulated current ramp is multiplexed and fed into the PWM comparator as shown in Figure 23. The valley current information is captured at the end of the off period, and the emulated current ramp is applied at that point when the next on cycle begins. An error amplifier integrates the error between the feedback voltage and the generated the error voltage from the COMP pin (from error amp in Figure 23).

Figure 23. Simplified Control Architecture

As shown in Figure 23, the emulated current ramp is generated inside the IC but offers programmability through the RAMPx pin. Selecting an appropriate value resistor from  $V_{\rm IN}$  to the RAMP pin programs a desired slope compensation value and, at the same time, provides a feed forward feature. The benefits realized by deploying this type of control scheme are that there is no need to worry about the turn-on current spike corrupting the current ramp. Also, the current signal is stable because the current signal is sampled at the end of the turn-off period, which gives time for the switch node ringing to settle. Other

benefits of using current mode control scheme still apply, such as simplicity of loop compensation. Control logic enforces antishoot-through operation to limit cross conduction of the internal drivers and external MOSFETs.

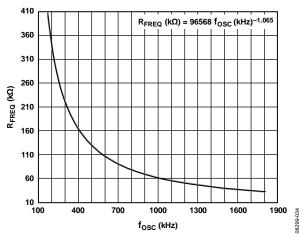

#### **OSCILLATOR FREQUENCY**

The internal oscillator frequency, which ranges from 200 kHz to 1.5 MHz, is set by an external resistor,  $R_{\text{FREQ}}$ , at the FREQ pin. Some popular  $f_{\text{OSC}}$  values are shown in Table 4, and a graphical relationship is shown in Figure 24. For instance, a 78.7 k $\Omega$  resistor sets the oscillator frequency to 800 kHz. Furthermore, connecting FREQ to AGND or FREQ to VCCO sets the oscillator frequency to 300 kHz or 600 kHz, respectively. For other frequencies that are not listed in Table 4, the values of  $R_{\text{FREQ}}$  and  $f_{\text{OSC}}$  can be obtained from Figure 24, or use the following empirical formula to calculate these values:

$$R_{EREO}(k\Omega) = 96568 \times f_{OSC} (kHz)^{-1.065}$$

**Table 4. Setting the Oscillator Frequency**

|                   | 1 /            |

|-------------------|----------------|

| R <sub>FREQ</sub> | fosc (Typical) |

| 332 kΩ            | 200 kHz        |

| 78.7 kΩ           | 800 kHz        |

| 60.4 kΩ           | 1000 kHz       |

| 51 kΩ             | 1200 kHz       |

| 40.2 kΩ           | 1500 kHz       |

| FREQ to AGND      | 300 kHz        |

| FREQ to VCCO      | 600 kHz        |

Figure 24. RFREQ vs. fosc

#### **MODE OF OPERATION**

The SYNC pin is a multifunctional pin. PWM mode is enabled when SYNC is connected to VCCO or a high logic. With SYNC connected to ground or left floating, pulse skip mode is enabled. Switching SYNC from low to high or high to low on the fly causes the controller to transition from forced PWM to pulse skip mode or pulse skip mode to forced PWM, respectively, in two clock cycles.

**Table 5. Mode of Operation Truth Table**

|              | _                 |

|--------------|-------------------|

| SYNC Pin     | Mode of Operation |

| Low          | Pulse skip mode   |

| High         | Forced PWM        |

| No Connect   | Pulse skip mode   |

| Clock Signal | Forced PWM        |

|              |                   |

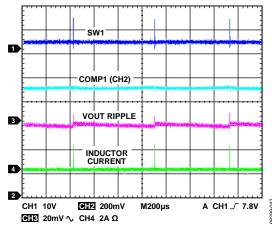

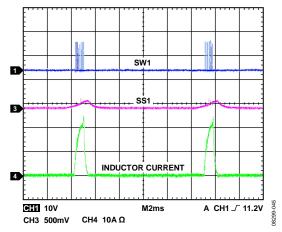

The ADP1877 has a built-in pulse skip sensing circuitry that allows the controller to skip PWM pulses, thus reducing the switching frequency at light loads and, therefore, maintaining high efficiency during a light load operation. The switching frequency is a fraction of the natural oscillator frequency and is automatically adjusted to regulate the output voltage. The resulting output ripple is larger than that of the fixed frequency forced PWM. Figure 25 shows that the ADP1877 operates in PSM under a light load of 10 mA. Pulse skip frequency under a certain light load is dependent on the inductor input and output voltages.

Figure 25. Example of Pulse Skip Mode Under a Light 5 mA Load

When the output load is greater than the pulse skip threshold current (when  $V_{\text{COMP}}$  reaches the threshold of 0.9 V), the ADP1877 exits the pulse skip mode operation and enters the fixed frequency discontinuous conduction mode (DCM), as shown in Figure 26. When the load increases further, the ADP1877 enters CCM.

Figure 26. Example of Discontinuous Conduction Mode (DCM) Waveform

In forced PWM, the ADP1877 always operates in CCM at any load. The inductor current is always continuous (and even goes negative when there is no load); thus, efficiency is poor at light loads.

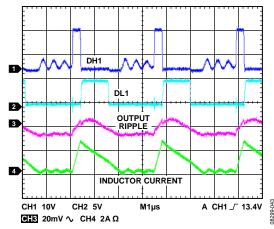

#### **SYNCHRONIZATION**

The switching frequency of the ADP1877 can be synchronized to an external clock by connecting SYNC to a clock signal, which should be between  $1\times$  and  $2.3\times$  of the internal oscillator frequency, fosc. The resulting switching frequency, fsw, is ½ of the external SYNC frequency because the SYNC input is divided by 2, and the resulting phases are used to clock the two channels alternately. In synchronization, the ADP1877 operates in PWM, and fsw equals ½ of fsync.

When an external clock is detected at the first SYNC edge, the internal oscillator is reset, and the clock control shifts to SYNC. The SYNC edges then trigger subsequent clocking of the PWM outputs. The DH1/DH2 rising edges appear approximately 100 ns after the corresponding SYNC edge, and the frequency is locked to the external signal. Depending on the start-up conditions of Channel 1 and Channel 2, either Channel 1 or Channel 2 can be the first channel synchronized to the rising edge of the SYNC clock. If the external SYNC signal disappears during operation, the ADP1877 reverts to its internal oscillator. When the SYNC function is used, it is recommended to connect a pull-up resistor from SYNC to VCCO so that when the SYNC signal is lost, the ADP1877 continues to operate in PWM.

#### **SOFT START**

The soft start period is set by an external capacitor between SS1/SS2 and AGND. When EN1/EN2 is enabled, a current source of 6.5  $\mu A$  starts charging the capacitor, and the regulation voltage is reached when the voltage at SS1/SS2 reaches 0.6 V. For more information, see the Applications Information section.

#### SYNCHRONOUS RECTIFIER AND DEAD TIME

The synchronous rectifier (low-side MOSFET) improves efficiency by replacing the Schottky diode that is normally used in an asynchronous buck regulator. In the ADP1877, the antishoot-through circuit monitors the SW and DL nodes and adjusts the low-side and high-side drivers to ensure break-before-make switching to prevent cross-conduction or shoot-through between the high-side and low-side MOSFETs. This break-before-make switching is known as the dead time, which is not fixed and depends on how fast the MOSFETs are turned on and off. In a typical application circuit that uses medium sized MOSFETs with input capacitance of approximately 3 nF, the typical dead time is approximately 30 ns. When small and fast MOSFETs are used, the dead time can be as low as 13 ns.

#### INPUT UNDERVOLTAGE LOCKOUT

When the bias input voltage,  $V_{\rm IN}$ , is less than the undervoltage lockout (UVLO) threshold, the switch drivers stay inactive. When  $V_{\rm IN}$  exceeds the UVLO threshold, the switchers start switching.

#### INTERNAL LINEAR REGULATOR

The internal linear regulator is low dropout (LDO), meaning it can regulate its output voltage, VCCO. VCCO powers up the internal control circuitry and provides power for the gate drivers. It is guaranteed to have more than 200 mA of output current capability, which is sufficient to handle the gate drive requirements of typical logic threshold MOSFETs driven at up to 1.5 MHz. VCCO is always active and cannot be shut down by the EN1/EN2 pins. Bypass VCCO to AGND with a 1  $\mu F$  or greater capacitor.

Because the LDO supplies the gate drive current, the output of VCCO is subject to sharp transient currents as the drivers switch and the boost capacitors recharge during each switching cycle. The LDO has been optimized to handle these transients without overload faults. Due to the gate drive loading, using the VCCO output for other external auxiliary system load is not recommended.

The LDO includes a current limit well above the expected maximum gate drive load. This current limit also includes a short-circuit fold back to further limit the VCCO current in the event of a short-circuit fault.

The VDL pin provides power to the low-side driver. Connect VDL to VCCO. Bypass VDL to PGND with a 1  $\mu$ F (minimum) ceramic capacitor, which must be placed close to the VDL pin.

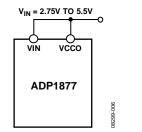

For an input voltage less than 5.5 V, it is recommended to bypass the LDO by connecting VIN to VCCO, as shown in Figure 27, thus eliminating the dropout voltage. However, for example, if the input range is 4 V to 7 V, the LDO cannot be bypassed by shorting VIN to VCCO because the 7 V input has exceeded the maximum voltage rating of the VCCO pin. In this case, use the LDO to drive the internal drivers, but keep in mind that there is a dropout when  $V_{\rm IN}$  is less than 5 V.

Figure 27. Configuration for  $V_{IN} < 5.5 V$

#### **OVERVOLTAGE PROTECTION**

The ADP1877 has a built-in circuit for detecting output overvoltage at the FB node. When the FB voltage,  $V_{\rm FB}$ , rises above the overvoltage threshold, the low-side NMOSFET is immediately turned on, and the high-side NMOSFET is turned off until the  $V_{\rm FB}$  drops below the undervoltage threshold. This action is known as the crowbar overvoltage protection. If the overvoltage condition is not removed, the controller maintains the feedback voltage between the overvoltage and undervoltage thresholds, and the output is regulated to within approximately +16% and -10% of the regulation voltage. During an overvoltage event, the SS node discharges toward zero through an internal 1 k $\Omega$  pull-down resistor. When the voltage at FB drops below the undervoltage threshold, the soft start sequence restarts. The following graph shows the overvoltage protection scheme in action in PSM.

Figure 28. Overvoltage Protection in PSM

#### **POWER GOOD**

The PGOODx pin is an open-drain NMOS with an internal  $12~k\Omega$  pull-up resistor connected between PGOODx and VCCO. PGOODx is internally pulled up to VCCO during normal operation and is active low when tripped. When the feedback voltage,  $V_{FB}$ , rises above the overvoltage threshold or drops below the undervoltage threshold, the PGOODx output is pulled to ground after a delay of  $12~\mu s$ . The overvoltage or undervoltage condition must exist for more than  $12~\mu s$  for PGOODx to become active. The PGOODx output also becomes active if a thermal overload condition is detected.

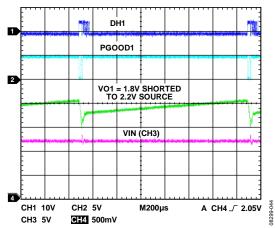

# SHORT CIRCUIT AND CURRENT LIMIT PROTECTION

When the output is shorted or the output current exceeds the current limit set by the  $R_{\rm ILIM}$  resistor for eight consecutive cycles, the ADP1877 shuts off both the high-side and low-side drivers and restarts the soft start sequence every 10 ms, which is known as hiccup mode. The SS node discharges to zero through an internal 1  $k\Omega$  resistor during an overcurrent or short-circuit event. Figure 29 shows that the ADP1877 (a 20 A application circuit) is entering current limit hiccup mode when the output is shorted.

Figure 29. Current Limit Hiccup Mode, 20 A Circuit

#### SHUTDOWN CONTROL

The EN1 and EN2 pins are used to enable or disable Channel 1 and Channel 2, respectively, of the ADP1877. The precision enable threshold for EN1/EN2 is typically 0.63 V. When the EN1/EN2 voltage rises above 0.63 V, the ADP1877 is enabled and starts normal operation after the soft start period. When the voltage at EN1/EN2 drops below 0.57 V, the switchers and the internal circuits in the ADP1877 are turned off. Note that EN1/EN2 cannot shut down the LDO at VCCO, which is always active.

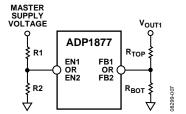

For the purpose of start-up power sequencing, the startup of the ADP1877 can be programmed by connecting an appropriate resistor divider from the master power supply to the EN1/EN2 pin, as shown in Figure 30. For instance, if the desired start-up voltage from the master power supply is 10 V, R1 and R2 can be set to 156  $k\Omega$  and 10  $k\Omega$ , respectively.

Figure 30. Optional Power-Up Sequencing Circuit

#### THERMAL OVERLOAD PROTECTION

The ADP1877 has an internal temperature sensor that senses the junction temperature of the chip. When the junction temperature of the ADP1877 reaches approximately 155°C, the ADP1877 goes into thermal shutdown, the converter is turned off, and SS discharges toward zero through an internal 1  $k\Omega$  resistor. At the same time, VCCO discharges to zero. When the junction temperature drops below 135°C, the ADP1877 resumes normal operation after the soft start sequence.

### APPLICATIONS INFORMATION

#### SETTING THE OUTPUT VOLTAGE

The output voltage is set using a resistive voltage divider from the output to FB. The voltage divider divides down the output voltage to the 0.6 V FB regulation voltage to set the regulation output voltage. The output voltage can be set to as low as 0.6 V and as high as 90% of the power input voltage.

The maximum input bias current into FB is 100 nA. For a 0.15% degradation in regulation voltage and with 100 nA bias current, the low-side resistor,  $R_{\text{BOT}}$ , must be less than 9 k $\Omega$ , which results in 67  $\mu\text{A}$  of divider current. For  $R_{\text{BOT}}$ , use a 1 k $\Omega$  to 20 k $\Omega$  resistor. A larger value resistor can be used but results in a reduction in output voltage accuracy due to the input bias current at the FB pin, while lower values cause increased quiescent current consumption. Choose  $R_{\text{TOP}}$  to set the output voltage by using the following equation:

$$R_{TOP} = R_{BOT} \left( \frac{V_{OUT} - V_{FB}}{V_{FB}} \right)$$

where:

$R_{TOP}$  is the high-side voltage divider resistance.  $R_{BOT}$  is the low-side voltage divider resistance.  $V_{OUT}$  is the regulated output voltage.  $V_{FB}$  is the feedback regulation threshold, 0.6 V.

The minimum output voltage is dependent on  $f_{SW}$  and minimum DH on time. The maximum output voltage is dependent on  $f_{SW}$ , the minimum DH off time, and the IR drop across the high-side N-channel MOSFET (NMOSFET) and the DCR of the inductor. For example, with an  $f_{SW}$  of 600 kHz (or 1.67  $\mu$ s) and minimum on time of 130 ns, the minimum duty cycle is approximately 7.8% (130 ns/1.67  $\mu$ s). If  $V_{IN}$  is 12 V and the duty cycle is 7.8%, then the lowest output is 0.94 V. As an example for the maximum output voltage, if  $V_{IN}$  is 5 V,  $f_{SW}$  is 600 kHz, and the minimum DH off time is 390 ns (330 ns DH off time plus approximately 60 ns total dead time), then the maximum duty cycle is 76%. Therefore, the maximum output is approximately 3.8 V. If the IR drop across the high-side NMOSFET and the DCR of the inductor is 0.5 V, then the absolute maximum output is 4.5 V (5 V – 0.5 V), independent of  $f_{SW}$  and duty cycle.

#### **SOFT START**

Program the soft start by connecting a capacitor from SSx to AGND. The soft start function limits the input inrush current and prevents the output overshoot.

On startup, a  $6.5 \mu A$  current source charges the SSx capacitor. The soft start period is approximated by

$$t_{SS} = \frac{0.6 V}{6.5 \, \mu A} C_{SS}$$

The SSx pin reaches a final voltage equal to VCCO. If the output voltage is precharged prior to turn-on, the ADP1877 prevents reverse inductor current, which discharges the output capacitor.

Once the voltage at SSx exceeds the regulation voltage (typically 0.6 V), the reverse current is reenabled to allow the output voltage regulation to be independent of load current.

When a controller is disabled, for instance, EN1/EN2 is pulled low or experiences an overcurrent limit condition, the soft start capacitor is discharged through an internal 1  $k\Omega$  pull-down resistor

#### **SETTING THE CURRENT LIMIT**

The current limit comparator measures the voltage across the low-side MOSFET to determine the load current.

The current limit is set by an external current limit resistor,  $R_{\rm ILIM}$ . The current sense pin, ILIMx, sources 50  $\mu A$  to this external resistor. This creates an offset voltage of  $R_{\rm ILIM}$  multiplied by 50  $\mu A$ . When the drop across the low-side MOSFET,  $R_{DSON}$ , is equal to or greater than this offset voltage, the ADP1877 flags a current limit event.

Because the ILIMx current and the MOSFET,  $R_{DSON}$ , vary over process and temperature, the minimum current limit should be set to ensure that the system can handle the maximum desired load current. To do this, use the peak current in the inductor, which is the desired output current limit level plus ½ of the ripple current, the maximum  $R_{DSON}$  of the MOSFET at its highest expected temperature, and the minimum ILIM current.

$$R_{\rm ILIM} = \frac{I_{\rm LPK} \times R_{\rm DSON\_MAX}}{40 \; \mu A}$$

where

$I_{LPK}$  is the peak inductor current.

The buck converters usually run a fairly high current. PCB layout and component placement may affect the current limit setting. An iteration of the  $R_{\rm ILIM}$  value may be required for a particular board layout and MOSFET selection. If alternative MOSFETs are substituted at some point in production, these resistor values may also need an iteration. Keep in mind that the temperature coefficient of the MOSFET,  $R_{DSON}$ , is typically 0.4%/°C.

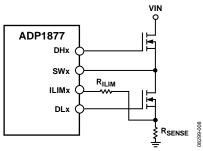

#### **ACCURATE CURRENT LIMIT SENSING**

$R_{DSON}$  of the MOSFET can vary by more than 50% over the temperature range. Accurate current limit sensing can be achieved by adding a current sense resistor from the source of the low-side MOSFET to PGND. Make sure that the power rating of the current sense resistor is adequate for the application. Apply the above equation and calculate  $R_{\rm ILIM}$  by replacing  $R_{\rm DSON\_MAX}$  with  $R_{\rm SENSE}$ . The Figure 31 illustrates the implementation of this accurate current limit sensing.

Figure 31. Accurate Current Limit Sensing

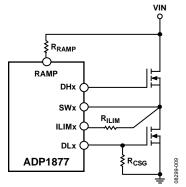

#### **SETTING THE SLOPE COMPENSATION**

In a current-mode control topology, slope compensation is needed to prevent subharmonic oscillations in the inductor current and to maintain a stable output. The external slope compensation is implemented by summing the amplified sense signal and a scaled voltage at the RAMPx pin. To implement the slope compensation, connect a resistor between RAMPx and the input voltage. The resistor, RRAMP, is calculated by

$$R_{RAMP} = \frac{3.6 \times 10^{10} L}{A_{CS} \times R_{DSON-MAX}}$$

where:

$3.6 \times 10^{10}$  is an internal parameter.

*L* is the inductance of the inductor.

$R_{DSON\_MAX}$  is the the low-side MOSFET maximum on resistance.  $A_{CS}$  is the gain, either 3 V/V, 6 V/V, 12 V/V, or 24 V/V, of the current sense amplifier (see the Setting the Current Sense Gain section for more details).

Keep in mind that  $R_{DSON}$  is temperature dependent and can vary as much as 0.4%/°C. Choose  $R_{DSON}$  at the maximum operating temperature. The voltage at RAMPx is fixed at 0.2 V, and the current going into RAMPx should be in between 6  $\mu$ A and 200  $\mu$ A. Make sure that the following condition is satisfied:

$$6\,\mu\mathrm{A} \leq \frac{V_\mathit{IN} - 0.2\mathrm{V}}{R_\mathit{RAMP}} \leq 200\,\mu\mathrm{A}$$

For instance, with an input voltage of 12 V,  $R_{RAMP}$  should not exceed 1.9 M $\Omega$ . If the calculated  $R_{RAMP}$  produces less than 6  $\mu$ A, then select a  $R_{RAMP}$  value that produces between 6  $\mu$ A and 20  $\mu$ A. Figure 32 illustrates the connection of the slope compensation resistor  $R_{RAMP}$  and the current sense gain resistor  $R_{CSG}$ .

Figure 32. Slope Compensation and CS Gain Connection

#### **SETTING THE CURRENT SENSE GAIN**

The voltage drop across the external low-side MOSFET is sensed by a current sense amplifier by multiplying the peak inductor current and the  $R_{\rm DSON}$  of the MOSFET. The result is then amplified by a gain factor of either 3 V/V, 6 V/V, 12 V/V, or 24 V/V, which is programmable by an external resistor,  $R_{\rm CSG}$ , connected to the DL pin. This gain is sensed only during power-up and not during normal operation. The amplified voltage is summed with the slope compensation ramp voltage and fed into the PWM controller for a stable regulation voltage.

The voltage range of the internal node,  $V_{CS}$ , is between 0.4 V and 2.2 V. Select the current sense gain such that the internal minimum amplified voltage ( $V_{CSMIN}$ ) is above 0.4 V and the maximum amplified voltage ( $V_{CSMAX}$ ) is 2.1 V. Do not set  $V_{CSMAX}$  above 2.1 V to account for temperature and part-to-part variations. Note that  $V_{CSMIN}$  or  $V_{CSMAX}$  is not the same as  $V_{COMP}$ , which has a range of 0.75 V to 2.25 V. The following are equations for  $V_{CSMIN}$  and  $V_{CSMAX}$ :

$$\begin{split} V_{CSMIN} &= 0.75 \ V - \frac{1}{2} I_{LPP} \times R_{DSON\_MIN} \times A_{CS} \\ \\ V_{CSMAX} &= 0.75 \ V + (I_{LOADMAX} + \frac{1}{2} I_{LPP}) \times R_{DSON\_MAX} \times A_{CS} \end{split}$$

where

$V_{CSMIN}$  is the minimum amplified voltage of the internal current sense amplifier at zero output current.

$V_{\text{CSMAX}}$  is the maximum amplified voltage of the internal current sense amplifier at maximum output current.

$R_{DSON\_MIN}$  is the the low-side MOSFET minimum on resistance. The zero-current level voltage of the current sense amplifier is 0.75 V.

$I_{LPP}$  is the peak-to-peak ripple current in the inductor.  $I_{LOADMAX}$  is the maximum output DC load current.

Table 6 shows the appropriate current sense gain settings for a given  $R_{\rm DSON}$  maximum load current and a 33% inductor current ripple. Because of the variation in  $R_{\rm DSON}$  of the power MOSFETs (part-to-part variation and overtemperature) and the variation of the inductors, the users must verify that  $V_{\rm COMP}$  does not exceed 2.2 V at the maximum output load current.

Table 6. CS Gain Setting Selection Table for Some Popular Configurations

| I <sub>LPP</sub> = 339   | % Load   | ACS                     | 5 = 3                   | ACS                     | S = 6                   | ACS                     | ACS = 12                |                         | = 24                    |

|--------------------------|----------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| $R_{DSON}$ (m $\Omega$ ) | Load (A) | V <sub>cs</sub> Min (V) | V <sub>cs</sub> Max (V) | V <sub>cs</sub> Min (V) | V <sub>cs</sub> Max (V) | V <sub>cs</sub> Min (V) | V <sub>cs</sub> Max (V) | V <sub>cs</sub> Min (V) | V <sub>cs</sub> Max (V) |

| 1.5                      | 25       | 0.73                    | 0.9                     | 0.71                    | 1.01                    | 0.7                     | 1.3                     | 0.6                     | 1.80                    |

| 2                        | 25       | 0.73                    | 0.9                     | 0.70                    | 1.10                    | 0.7                     | 1.4                     |                         |                         |

| 2                        | 20       | 0.73                    | 0.9                     | 0.71                    | 1.03                    | 0.7                     | 1.3                     |                         |                         |

| 3                        | 20       | 0.72                    | 1.0                     | 0.69                    | 1.17                    | 0.6                     | 1.6                     |                         |                         |

| 5                        | 15       | 0.71                    | 1.0                     | 0.68                    | 1.27                    | 0.6                     | 1.8                     |                         |                         |

| 7                        | 10       | 0.72                    | 1.0                     | 0.68                    | 1.24                    | 0.6                     | 1.7                     |                         |                         |

| 10                       | 10       | 0.70                    | 1.1                     | 0.65                    | 1.45                    |                         |                         |                         |                         |

| 15                       | 8        | 0.69                    | 1.2                     | 0.63                    | 1.59                    |                         |                         |                         |                         |

| 18                       | 8        | 0.68                    | 1.3                     | 0.61                    | 1.76                    |                         |                         |                         |                         |

| 20                       | 7        | 0.68                    | 1.2                     | 0.61                    | 1.73                    |                         |                         |                         |                         |

| 25                       | 5        | 0.69                    | 1.2                     | 0.63                    | 1.62                    |                         |                         |                         |                         |

| 30                       | 5        | 0.68                    | 1.3                     | 0.60                    | 1.80                    |                         |                         |                         |                         |

| 40                       | 5        | 0.65                    | 1.4                     |                         |                         |                         |                         |                         |                         |

| 60                       | 3        | 0.66                    | 1.4                     |                         |                         |                         |                         |                         |                         |

| 80                       | 2        | 0.67                    | 1.3                     |                         |                         |                         |                         |                         |                         |

| 100                      | 2        | 0.65                    | 1.4                     |                         |                         |                         |                         |                         |                         |

| 120                      | 2        | 0.63                    | 1.6                     |                         |                         |                         |                         |                         |                         |

#### INPUT CAPACITOR SELECTION

The input current to a buck converter is a pulse waveform. It is zero when the high-side switch is off and approximately equal to the load current when it is on. The input capacitor carries the input ripple current, allowing the input power source to supply only the direct current. The input capacitor needs sufficient ripple current rating to handle the input ripple, as well as an ESR that is low enough to mitigate input voltage ripple. For the usual current ranges for these converters, it is good practice to use two parallel capacitors placed close to the drains of the high-side switch MOSFETs (one bulk capacitor of sufficiently high current rating and a 10  $\mu F$  ceramic decoupling capacitor, typically).

Select an input bulk capacitor based on its ripple current rating. First, determine the duty cycle of the output.

$$D = \frac{V_{OUT}}{V_{IN}}$$

The input capacitor RMS ripple current is given by

$$I_{RMS} = I_O \sqrt{D(1-D)}$$

where:

$I_0$  is the output current.

*D* is the duty cycle

The minimum input capacitance required for a particular load is

$$C_{\mathit{IN},\mathit{MIN}} = \frac{I_{\mathit{O}} \times D(1-D)}{(V_{\mathit{PP}} - I_{\mathit{O}} \times DR_{\mathit{ESR}}) f_{\mathit{SW}}}$$

where:

$V_{PP}$  is the desired input ripple voltage.  $R_{ESR}$  is the equivalent series resistance of the capacitor. If an MLCC capacitor is used, the ESR is near 0, then the equation is simplified to

$$C_{IN,MIN} = I_O \times \frac{D(1-D)}{V_{PP} \times f_{SW}}$$

The capacitance of MLCC is voltage dependent. The actual capacitance of the selected capacitor must be derated accordingly. In addition, add more bulk capacitance, such as by using electrolytic or polymer capacitors, as necessary for large step load transisents. Make sure the current ripple rating of the bulk capacitor exceeds the minimum input current ripple of a particular design.

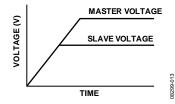

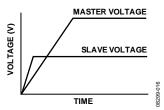

#### **INPUT FILTER**