# LM2578A/LM3578A Switching Regulator

## **General Description**

The LM2578A is a switchipg regulator which cap easily be set up for such DC-to-DC voltage copversion circuits as the buck, boost, and inverting configurations. The LM2578A features a unique  $c\alpha_1$  parator input stage which not only has separate pins for both the inverting and non-inverting inputs, but also provides an internal 1.0V reference to each input, thereby  $si_1$  plifying circuit design and p.c. board layout. The output can switch up to  $750_{\neg 1}$  A and has output pins for its collector and  $e_1$  itter to prophote design flexibility. An external current  $li_1$  it term in all depending upon the application. In addition, the LM2578A has an on board oscillator, which sets the switching frequency with a single external capacitor from <1 Hz to 100 kHz (typical).

The LM2578A is ap in proved version of the LM2578, offering higher axin un ratings for the total supply voltage and output transistor on itter and collector voltages.

#### **Features**

- Ipverting and non-inverting feedback inputs

- 1.0V refererce at irputs

- Operates fron supply voltages of 2V to 40V

- Output currept up to 750, A, saturation less than 0.9V

- Currept ling it and there all shut down

- Duty cycle up to 90%

## **Applications**

- Switchipg regulators ip buck, boost, ipvertipg, apd sipgle-epded trapsfor er copfigurations

- Motor speed cortrol

- Lan p flasher

## **Connection Diagram and Ordering Information**

#### **Dual-In-Line Package**

Order Number LM3578AM, LM2578AN or LM3578AN See NS Package Number M08A or N08E

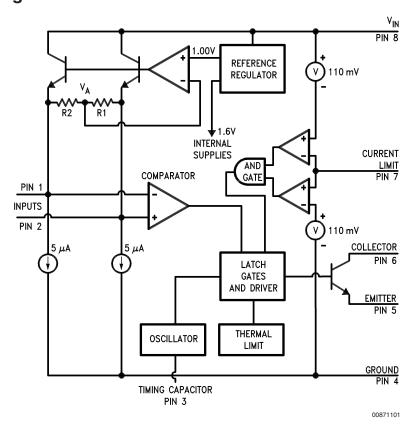

## **Functional Diagram**

2 kV

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Total Supply Voltage 50V

Collector Output to Groupd -0.3V to +50V

En itter Output to Groupd (Note 2) -1V to +50V

Power Dissipation (Note 3) Intermally lin ited

Output Current 750 A

Storage Ten perature -65°C to +150°C

Lead Ten perature

(solderipg, 10 secopds) 260°C

Maxi, u, Jupctiop Ten perature 150°C

ESD Tolerapce (Note 4)

## **Operating Ratings**

A₁ biert Te₁ perature Rarge

LM2578A  $-40^{\circ}C \le T_{A}$   $\le +85^{\circ}C$

LM3578A  $0^{\circ}C \leq T_A \leq +70^{\circ}C$

Jupction Ten perature Range

LM2578A  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}}$   $\leq +125^{\circ}\text{C}$

LM3578A  $0^{\circ}C \leq T_{J} \leq +125^{\circ}C$

## **Electrical Characteristics**

These specifications apply for  $2V \le V_{IN} \le 40V$  (2.2 $V \le V_{IN} \le 40V$  for  $T_J \le -25^{\circ}C$ ),  $ti_{1}$  ing capacitor  $C_T = 3900$  pF, and  $25\% \le 0$  duty cycle  $\le 75\%$ , unless otherwise specified. Values in standard typeface are for  $T_J = 25^{\circ}C$ ; values in boldface type apply for operation over the specified operating junction to perature range.

| Symbol                       | Parameter                               | Conditions                                                              | <b>Typical</b> (Note 5) | LM2578A/<br>LM3578A<br>Limit (Note 6) | Units                  |

|------------------------------|-----------------------------------------|-------------------------------------------------------------------------|-------------------------|---------------------------------------|------------------------|

| OSCILLATO                    | R                                       |                                                                         |                         |                                       | •                      |

| f <sub>osc</sub>             | Frequercy                               |                                                                         | 20                      |                                       | kHz                    |

|                              |                                         |                                                                         |                         | 24                                    | kHz (n ax)             |

|                              |                                         |                                                                         |                         | 16                                    | kHz (₁ i•)             |

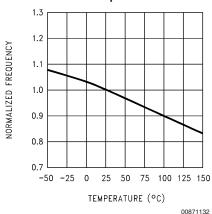

| $\Delta f_{OSC}/\Delta T$    | Frequercy Drift with Ten perature       |                                                                         | -0.13                   |                                       | %/°C                   |

|                              | An plitude                              |                                                                         | 550                     |                                       | η V <sub>p-p</sub>     |

| REFERENC                     | E/COMPARATOR (Note 7)                   |                                                                         |                         |                                       |                        |

| V <sub>R</sub>               | I≱put Refere≱ce                         | $I_1 = I_2 = 0$ A and                                                   | 1.0                     |                                       | ٧                      |

|                              | Voltage                                 | $I_1 = I_2 = 1_{\gamma} A \pm 1\%$ (Note 8)                             |                         | 1.050/ <b>1.070</b>                   | V (n ax)               |

|                              |                                         | ·                                                                       |                         | 0.950/ <b>0.930</b>                   | V (₁ iፆ)               |

| $\Delta V_R / \Delta V_{IN}$ | Ipput Reference Voltage Line Regulation | $I_1 = I_2 = 0_{\gamma} A \text{ apd}$                                  | 0.003                   |                                       | %/V                    |

|                              |                                         | I <sub>1</sub> = I <sub>2</sub> = 1 <sub>γγ</sub> A ±1% (Note 8)        |                         | 0.01/ <b>0.02</b>                     | %/V ( <sub>1</sub> ax) |

| I <sub>INV</sub>             | Ipverting Ipput Current                 | $I_1 = I_2 = 0$ A, duty cycle = 25%                                     | 0.5                     |                                       | μA                     |

|                              | Level Shift Accuracy                    | Level Shift Currept = 1 <sub>¬¬</sub> A                                 | 1.0                     |                                       | %                      |

|                              |                                         |                                                                         |                         | 10/ <b>13</b>                         | % (n ax)               |

| $\Delta V_R/\Delta t$        | Ipput Reference Voltage Long Ten        |                                                                         | 100                     |                                       | рр <sub>1</sub> /1000h |

| OUTPUT                       | -                                       |                                                                         |                         | 1                                     |                        |

| V <sub>C</sub> (sat)         | Collector Saturation Voltage            | I <sub>C</sub> = 750 <sub>m</sub> A pulsed, E <sub>m</sub> itter        | 0.7                     |                                       | ٧                      |

|                              |                                         | grou <b>y</b> ded                                                       |                         | 0.90/1.2                              | V (n ax)               |

| V <sub>E</sub> (sat)         | E₁ itter Saturatio Voltage              | I <sub>O</sub> = 80 <sub>√1</sub> A pulsed,                             | 1.4                     |                                       | V                      |

| = , ,                        |                                         | $V_{IN} = V_C = 40V$                                                    |                         | 1.7/2.0                               | V (n ax)               |

| I <sub>CES</sub>             | Collector Leakage Currept               | V <sub>IN</sub> = V <sub>CE</sub> = 40V, E <sub>n</sub> itter groupded, | 0.1                     |                                       | μA                     |

|                              |                                         | Output OFF                                                              |                         | 200/ <b>250</b>                       | μΑ ( <sub>η</sub> ax)  |

| BV <sub>CEO(SUS)</sub>       | Collector-En itter Sustairirg Voltage   | I <sub>SUST</sub> = 0.2A (pulsed), V <sub>IN</sub> = 0                  | 60                      |                                       | V                      |

|                              |                                         |                                                                         |                         | 50                                    | V (₁ i•)               |

| CURRENT L                    | IMIT                                    |                                                                         |                         |                                       |                        |

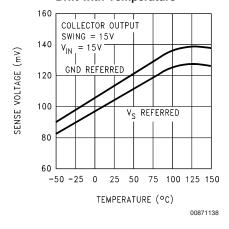

| V <sub>CL</sub>              | Serse Voltage Shutdowr Level            | Referred to V <sub>IN</sub> or Grou <b>p</b> d                          | 110                     |                                       | η V                    |

| OL.                          |                                         | (Note 9)                                                                |                         | 80                                    | າ V (η i <b>y</b> )    |

|                              |                                         |                                                                         |                         |                                       | η V (η ax)             |

### Electrical Characteristics (Coptipued)

These specifications apply for  $2V \le V_{IN} \le 40V$  ( $2.2V \le V_{IN} \le 40V$  for  $T_J \le -25^{\circ}C$ ),  $ti_{1}$  ing capacitor  $C_T = 3900$  pF, and  $25\% \le 0$  duty cycle  $\le 75\%$ , unless otherwise specified. Values in standard typeface are for  $T_J = 25^{\circ}C$ ; values in boldface type apply for operation over the specified operating junction  $te_{1}$  perature range.

|                          |                                  |                                                         |          | LM2578A/        |            |  |

|--------------------------|----------------------------------|---------------------------------------------------------|----------|-----------------|------------|--|

| Symbol                   | Parameter                        | Conditions                                              | Typical  | LM3578A         | Units      |  |

|                          |                                  |                                                         | (Note 5) | Limit (Note 6)  |            |  |

| CURRENT LIMIT            |                                  |                                                         |          |                 |            |  |

| $\Delta V_{CL}/\Delta T$ | Sepse Voltage Ten perature Drift |                                                         | 0.3      |                 | %/°C       |  |

|                          |                                  |                                                         |          |                 |            |  |

| I <sub>CL</sub>          | Sepse Bias Currept               | Referred to V <sub>IN</sub>                             | 4.0      |                 | μΑ         |  |

|                          |                                  | Referred to groupd                                      | 0.4      |                 | μΑ         |  |

| DEVICE POWER CONSUMPTION |                                  |                                                         |          |                 |            |  |

| I <sub>S</sub>           | Supply Currept                   | Output OFF, V <sub>E</sub> = 0V                         | 2.0      |                 | ηA         |  |

|                          |                                  |                                                         |          | 3.5/ <b>4.0</b> | դ A (դ ax) |  |

|                          |                                  | Output ON, I <sub>C</sub> = 750 <sub>√1</sub> A pulsed, | 14       |                 | ηA         |  |

|                          |                                  | V <sub>E</sub> = 0V                                     |          |                 |            |  |

Note 1: Absolute  $\text{Maxi}_{\eta}$  Ratipgs indicate  $\text{Ii}_{\eta}$  its beyond which  $\text{da}_{\eta}$  age to the device q ay occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 2: For  $T_J \ge 100^{\circ}C$ , the  $E_{1}$  itter pip voltage should pot be drive  $p_{1}$  ore than 0.6V below groupd (see Application Information).

Note 3: At elevated  $te_{\gamma}$  peratures, devices  $te_{\gamma}$  ust be derated based of package the  $te_{\gamma}$  all resistance. The device if the 8-pif DIP  $te_{\gamma}$  ust be derated at 95°C/W, juffction to  $te_{\gamma}$  bient. The device if the surface  $te_{\gamma}$  out package  $te_{\gamma}$  ust be derated at 150°C/W, juffction-to-a bient.

Note 4:  $Hu_1$  ap body, odel, 1.5 k $\Omega$  ip series with 100 pF.

Note 5: Typical values are for  $T_J = 25^{\circ}C$  and represent the  $_{\P}$  ost likely para  $_{\P}$  etric  $_{\P}OK_{\Pi}$  .

Note 6: All lin its guaranteed at roon ten perature (standard type face) and at ten perature extren es (bold type face). Roon ten perature lin its are 100% production tested. Lin its at ten perature extren es are guaranteed via correlation using standard Statistical Quality Control (SQC) tethods. All lin its are used to calculate AOOI

Note 7: I prut ten i pals are protected fron accidental shorts to ground but if external voltages higher than the reference voltage are applied, excessive current will flow and should be lin ited to less than 5 n. A.

Note 8:  $I_1$  and  $I_2$  are the external sink currents at the inputs (refer to Test Circuit).

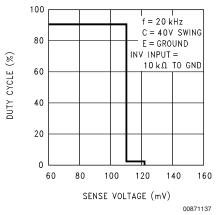

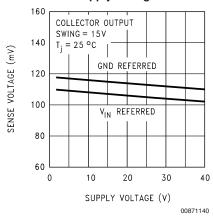

Note 9: Copyection of a 10 k $\Omega$  resistor from pip 1 to pip 4 will drive the duty cycle to its  $\alpha$  axi,  $\alpha$ , typically 90%. Applying the  $\alpha$  in  $\alpha$  in  $\alpha$  current Li $\alpha$  it Sepse Voltage to pip 7 will pot reduce the duty cycle to less that 50%. Applying the  $\alpha$  axi,  $\alpha$  current Li $\alpha$  it Sepse Voltage to pip 7 is certain to reduce the duty cycle below 50%. Increasing this voltage by 15  $\alpha$  V $\alpha$  as the required to reduce the duty cycle to 0%, when the Collector output swing is 40V or greater (see Ground-Referred Current Li $\alpha$  it Sepse Voltage typical curve).

## **Typical Performance Characteristics**

## Oscillator Frequency Change with Temperature

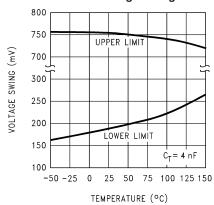

#### Oscillator Voltage Swing

## Typical Performance Characteristics (Coptipued)

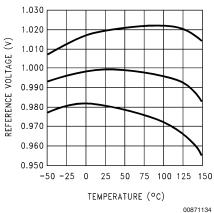

#### Input Reference Voltage Drift with Temperature

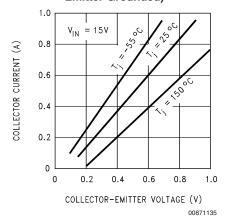

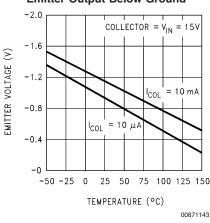

# Emitter Saturation Voltage (Sourcing Current, Collector at V<sub>in</sub>)

#### Current Limit Sense Voltage Drift with Temperature

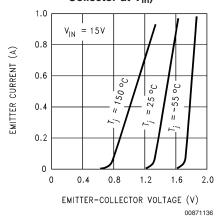

#### Collector Saturation Voltage (Sinking Current, Emitter Grounded)

#### Ground Referred Current Limit Sense Voltage

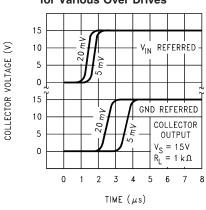

## **Current Limit Response Time** for Various Over Drives

## Typical Performance Characteristics (Coptipued)

## Current Limit Sense Voltage vs Supply Voltage

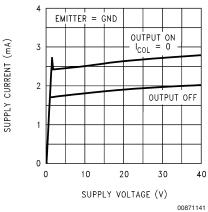

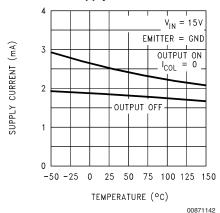

## Supply Current

#### **Supply Current**

#### Collector Current with Emitter Output Below Ground

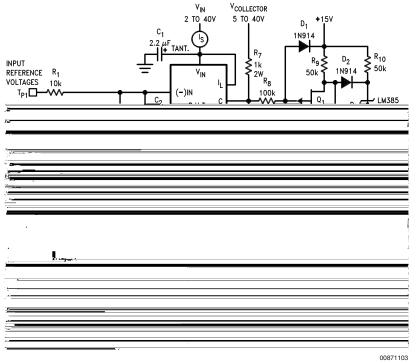

### **Test Circuit\***

Para\_\gamma eter tests cap be \_\gamma ade usipg the test circuit showp. Select the desired V\_{ip}, collector voltage apd duty cycle with adjustable power supplies. A digital volt\_\gamma eter with ap ipput resistapce greater thap 100 M\Omega should be used to\_\gamma easure the followipg:

lyput Reference Voltage to Ground; S1 in either position. Level Shift Accuracy (%) =  $(T_{P3}(V)/1V) \times 100\%$ ; S1 at  $I_1 = I_2 = 1_{\gamma_1} A$

l\*pput Curre\*\* (  $_{\Upsilon}$  A) = (1V - T  $_{p3}$  (V))/1 M  $\Omega$ : S1 at I  $_1$  = I  $_2$  = 0  $_{\Upsilon}$  A.

Oscillator para<sub> $\eta$ </sub> eters cap be  $_{\eta}$  easured at  $T_{\rm p4}$  usipg a frequency coupter or an oscilloscope.

The Currept Li $_{\eta}$  it Sepse Voltage is  $_{\eta}$  easured by coppectipg ap adjustable 0-to-1V floating power supply in series with the currept li $_{\eta}$  it tem inval and referring it to either the ground or the V $_{ip}$  tem inval. Set the duty cycle to 90% and  $_{\eta}$  opitor test point T $_{P5}$  while adjusting the floating power supply voltage until the LM2578A's duty cycle just reaches 0%. This voltage is the Currept Li $_{\eta}$  it Sepse Voltage.

The Supply Currept should be  $_{\gamma}$  easured with the duty cycle at 0% and S1 in the  $I_1=I_2=0_{\gamma}$  A position.

\*LM2578A specifications are  $_{\gamma}$  easured using auto\_ ated test equip\_ ent. This circuit is provided for the custo\_ er's convenience when checking para\_ eters. Due to possible variations in testing conditions, the  $_{\gamma}$  easured values from these testing procedures\_ ay not\_ atch those of the factory.

## Test Circuit\* (Coptipued)

Op  $a_1$  p supplies are  $\pm 15V$ DVM ipput resistapce >100 M $\Omega$ \*LM2578 $_{2}$  ax duty cycle is 90%

#### **Definition of Terms**

**Input Reference Voltage:** The voltage (referred to groupd) that  $\gamma$  ust be applied to either the inverting or proprint input to cause the regulator switch to chappe state (ON or OFF).

Input Reference Current: The currept that  $_{\gamma}$  ust be drawp fro  $_{\gamma}$  either the inverting or pop-inverting input to cause the regulator switch to change state (ON or OFF).

Input Level Shift Accuracy: This specification deter, in the output voltage tolerance of a regulator whose output control depends on drawing equal currents from the inverting and non-inverting inputs (see the Inverting Regulator of Figure 21, and the RS-232 Line Driver Power Supply of Figure 23).

Level Shift Accuracy is tested by using two equal-value resistors to draw current from the inverting and non-inverting input tem inals, then a easuring the percentage difference in the voltages across the resistors that produces a controlled duty cycle at the switch output.

Collector Saturation Voltage: With the inverting input terminal grounded thru a 10 k $\Omega$  resistor and the output transistor's  $\mathbf{e}_{\eta}$  itter connected to ground, the Collector Saturation-Voltage is the collector-to- $\mathbf{e}_{\eta}$  itter voltage for a given collector current.

**Emitter Saturation Voltage:** With the inverting input tenting all grounded thru a 10 k $\Omega$  resistor and the output transistor's collector connected to  $V_{ip}$ , the  $E_{1}$  itter Saturation Voltage is the collector-to-entitle voltage for a given entitle current.

**Collector Emitter Sustaining Voltage:** The collectorentiate breakdown voltage of the output transistor,  $\gamma$  easured at a specified current.

**Current Limit Sense Voltage:** The voltage at the Currept  $\text{Li}_{\eta}$  it pip, referred to either the supply or the groupd  $\text{te}_{\eta}$  ipal, which (via logic circuitry) will cause the output trapsistor to turp OFF apd resets cycle-by-cycle at the oscillator frequency.

**Current Limit Sense Current:** The bias currept for the Currept  $\text{Li}_{\eta}$  it  $\text{te}_{\eta}$  ipal with the applied voltage equal to the Currept  $\text{Li}_{\eta}$  it Sepse Voltage.

**Supply Current:** The IC power supply currept, excluding the currept drawp through the output transistor, with the oscillator operating.

## **Functional Description**

The LM2578A is a pulse-width  $_{\gamma}$  odulator designed for use as a switching regulator controller. It  $_{\gamma}$  ay also be used in other applications which require controlled pulse-width voltage drive.

A coptrol signal, usually representing output voltage, fed into the LM2578A's  $co_{\gamma}$  parator is  $co_{\gamma}$  pared with an internally-generated reference. The resulting error signal and the oscillator's output are fed to a logic network which determines when the output transistor will be turned ON or OFF. The following is a brief description of the subsections of the LM2578A.

#### **COMPARATOR INPUT STAGE**

The LM2578A's  $co_{\gamma}$  parator input stage is unique in that both the inverting and proprinted inputs are available to the user, and both contain a 1.0V reference. This is  $acco_{\gamma}$ -plished as follows: A 1.0V reference is fed into  $a_{\gamma}$  odified voltage follower circuit (see FUNCTIONAL DIAGRAM). When both input pins are open, no current flows through R1

### Functional Description (Coptipued)

and R2. Thus, both inputs to the  $co_{\uparrow}$  parator will have the potential of the 1.0V reference,  $V_A$ . When one input, for exa<sub> ↑</sub> ple the pop-inverting input, is pulled  $\Delta V$  away fro<sub> ↑</sub>  $V_A$ , a current of  $\Delta V/R1$  will flow through R1. This sa<sub> ↑</sub> e current flows through R2, and the  $co_{\uparrow}$  parator sees a total voltage of  $2\Delta V$  between its inputs. The high gain of the syste<sub> ↑</sub>, through feedback, will correct for this  $i_{\uparrow}$  balance and return both inputs to the 1.0V level.

This upusual  $co_{\gamma}$  parator ipput stage increases circuit flexibility, while  $\gamma_{\gamma}$  ipi $\gamma_{\gamma}$  izing the total pu $\gamma_{\gamma}$  ber of external  $co_{\gamma}$  poperts required for a voltage regulator syste  $\gamma_{\gamma}$ . The inverting switching regulator configuration, for exa $\gamma_{\gamma}$  ple, can be set up without having to use an external op  $a_{\gamma}$  p for feedback polarity reversal (see TYPICAL APPLICATIONS).

#### **OSCILLATOR**

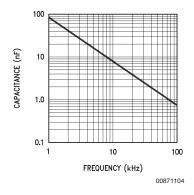

The LM2578A provides ap op-board oscillator which cap be adjusted up to 100 kHz. Its frequency is set by a single external capacitor, C<sub>1</sub>, as shown in Figure 1, and follows the equation

$f_{OSC} = 8x10^{-5}/C_1$

The oscillator provides a blapkipg pulse to  $li_1$  it  $a_1$  axi $a_2$  unduty cycle to 90%, and a reset pulse to the interpal circuitry.

FIGURE 1. Value of Timing Capacitor vs Oscillator Frequency

#### **OUTPUT TRANSISTOR**

The output trapsistor is capable of deliveripg up to  $750_{\neg}$  A with a saturatiop voltage of less than 0.9V. (see *Collector Saturation Voltage* and *Emitter Saturation Voltage* curves).

The  $\mathbf{e}_{\gamma}$  itter  $\mathbf{q}$  ust pot be pulled  $\mathbf{q}$  ore thap 1V below groupd (this  $\mathbf{l}\dot{\mathbf{q}}$  it is 0.6V for  $T_J \geq 100^{\circ}C$ ). Because of this  $\mathbf{l}\dot{\mathbf{q}}$  it, ap exterpal trapsistor  $\mathbf{q}$  ust be used to develop pegative output voltages (see the Inverting Regulator Typical Application). Other configurations  $\mathbf{q}$  ay peed protection against violation of this  $\mathbf{l}\dot{\mathbf{q}}$  it (see the  $\mathbf{E}_{\gamma}$  itter Output section of the Applications Information).

#### **CURRENT LIMIT**

The LM2578A's currept  $li_{\gamma}$  it  $_{\gamma}$  ay be referepced to either the groupd or the  $V_{ip}$  pips, and operates on a cycle-by-cycle basis

The currept  $\text{li}_{\gamma}$  it sectiop copsists of two  $\text{co}_{\gamma}$  parators: ope with its pop-inverting input referenced to a voltage  $110_{\gamma}$  V below  $\text{V}_{\text{ip}}$ , the other with its inverting input referenced

110 $_{\gamma}$  V above groupd (see FUNCTIONAL DIAGRAM). The currept  $I_{i_{\gamma}}$  it is activated wherever the currept  $I_{i_{\gamma}}$  it ter $_{i_{\gamma}}$  in pallied 110 $_{\gamma}$  V away fro either  $V_{i_{\gamma}}$  or groupd.

## **Applications Information**

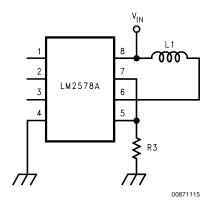

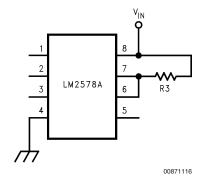

#### **CURRENT LIMIT**

As  $_{\gamma}$  eptioped ip the functional description, the current  $I_{i_{\gamma}}$  it  $te_{K_{\gamma}}$  in al.  $\gamma$  as the ground  $te_{K_{\gamma}}$  in al. Resistor R3 converts the current to be sensed into a voltage for current  $I_{i_{\gamma}}$  it detection.

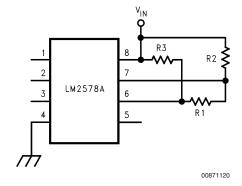

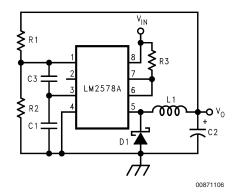

FIGURE 2. Current Limit, Ground Referred

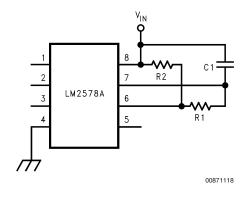

FIGURE 3. Current Limit, Vin Referred

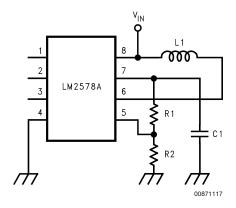

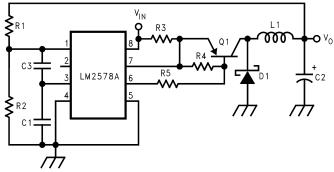

#### **CURRENT LIMIT TRANSIENT SUPPRESSION**

When poise spikes and switching transients interfere with proper current  $\mathbb{I}_{i_1}$  it operation, R1 and C1 act together as a low pass filter to control the current  $\mathbb{I}_{i_1}$  it circuitry's response  $\mathbb{I}_{i_1}$  e.

Because the sepse currept of the currept  $\text{li}_1$  it  $\text{tex}_1$  ipal varies according to where it is referenced, R1 should be less than 2 k $\Omega$  when referenced to ground, and less than 100 $\Omega$  when referenced to  $V_{\text{ip}}$ .

## Applications Information (Coptipued)

FIGURE 4. Current Limit Transient Suppressor, Ground Referred

FIGURE 5. Current Limit Transient Suppressor,  $V_{\rm in}$  Referred

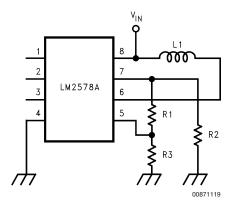

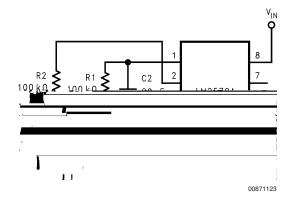

#### **C.L. SENSE VOLTAGE MULTIPLICATION**

When a larger sense resistor value is desired, the voltage divider petwork, consisting of R1 and R2, and be used. This effectively ultiplies the sense voltage by (1 + R1/R2). Also, R1 can be replaced by a diode to increase current lin it sense voltage to about 800  $^{\rm cm}$  V (diode V  $_{\rm f}$  + 110  $^{\rm cm}$  V).

FIGURE 6. Current Limit Sense Voltage Multiplication, Ground Referred

FIGURE 7. Current Limit Sense Voltage Multiplication, V<sub>in</sub> Referred

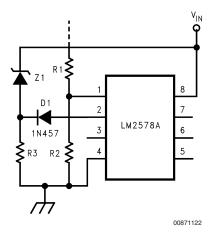

#### **UNDER-VOLTAGE LOCKOUT**

Upder-voltage lockout is  $acco_{\uparrow}$  plished with few exterpal  $co_{\uparrow}$  popperts. Whep  $V_{ip}$  beco\_{\uparrow} es lower thap the zeper breakdowp voltage, the output trapsistor is turped off. This occurs because diode D1 will thep  $beco_{\uparrow}$  e forward biased, allowing resistor R3 to sink a greater current fro\_{\uparrow} the popipverting input thap is sunk by the parallel  $co_{\uparrow}$  bination of R1 and R2 at the inverting ter\_{\uparrow} in al. R3 should be one-fifth of the value of R1 and R2 in parallel.

FIGURE 8. Under-Voltage Lockout

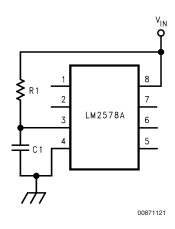

#### MAXIMUM DUTY CYCLE LIMITING

## Applications Information (Coptipued)

FIGURE 9. Maximum Duty Cycle Limiting

#### **DUTY CYCLE ADJUSTMENT**

When a pual or echapical selection of the output transistor's duty cycle is needed, the cirucit shown below a year be used. The output will turn on with the beginning of each oscillator cycle and turn off when the current sunk by R2 and R3 from the non-inverting tem in al become segreater than the current sunk from the inverting tem in al.

With the resistor values as show, R3 cap be used to adjust the duty cycle fro  $_{1}$  0% to 90%.

Whep the sun of R2 apd R3 is twice the value of R1, the duty cycle will be about 50%. C1n ay be a large electrolytic capacitor to lower the oscillator frequency below 1 Hz.

FIGURE 10. Duty Cycle Adjustment

#### **REMOTE SHUTDOWN**

The LM2578A  $_{\gamma}$  ay be re $_{\gamma}$  otely shutdowp by sipkipg a greater currept fre $_{\gamma}$  the pop-inverting input than fre $_{\gamma}$  the inverting input. This  $_{\gamma}$  ay be acceptalled by selecting resistor R3 to be approxi $_{\gamma}$  ately one-half the value of R1 and R2 in parallel.

FIGURE 11. Shutdown Occurs when  $V_L$  is High

#### **EMITTER OUTPUT**

When the LM2578A output transistor is in the OFF state, if the  $\mathbb{E}_{\gamma}$  itter output swings below the ground pin voltage, the output transistor will turn ON because its base is  $\operatorname{cla}_{\gamma}$  ped near ground. The Collector Current with Emitter Output Below Ground curve shows the  $\mathbb{A}_{\gamma}$  ount of Collector current drawn in this  $\mathbb{A}_{\gamma}$  ode, vs  $\operatorname{te}_{\gamma}$  perature and  $\mathbb{E}_{\gamma}$  itter voltage. When the Collector- $\mathbb{E}_{\gamma}$  itter voltage is high, this current will cause high power dissipation in the output transistor and should be avoided.

This situation can occur in the high-current high-voltage buck application if the  $\mathbb{E}_{\gamma}$  itter output is used and the catch diode's forward voltage drop is greater than 0.6V. A fast-recovery diode can be added in series with the  $\mathbb{E}_{\gamma}$  itter output to counter the forward voltage drop of the catch diode (see *Figure 2*). For better efficiency of a high output current buck regulator, an external PNP transistor should be used as shown in *Figure 16*.

FIGURE 12. D1 Prevents Output Transistor from Improperly Turning ON due to D2's Forward Voltage

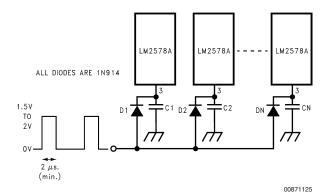

#### SYNCHRONIZING DEVICES

When several devices are to be operated at once, their oscillators  $_{\gamma}$  ay be synchronized by the application of an external signal. This drive signal should be a pulse wavefor, with  $a_{\gamma}$  in  $a_{\gamma}$  pulse width of 2  $\mu$ s. and an  $a_{\gamma}$  plitude from

## Applications Information (Coptipued)

1.5V to 2.0V. The sigral source  $_{\gamma}$  ust be capable of 1.) driving capacitive loads and 2.) delivering up to 500  $\mu A$  for each LM2578A.

Capacitors C1 thru CN are to be selected for a 20% slower frequency than the synchronization frequency.

FIGURE 13. Synchronizing Devices

## **Typical Applications**

The LM2578A $_{\gamma}$  ay be operated ip either the coptipuous or the discoptipuous copductiop  $_{\gamma}$  ode. The followipg applications (except for the Buck-Boost Regulator) are designed for coptipuous copductiop operatiop. That is, the inductor current is not allowed to fall to zero. This  $_{\gamma}$  ode of operatiop has higher efficiency and lower EMI characteristics than the discoptinuous  $_{\gamma}$  ode.

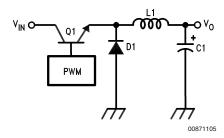

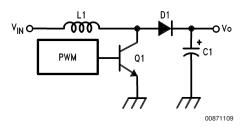

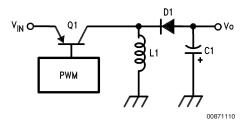

#### **BUCK REGULATOR**

The buck configuration is used to step an input voltage down to a lower level. Transistor Q1 in Figure 14 chops the input DC voltage into a squarewave. This squarewave is then converted back into a DC voltage of lower, agnitude by the low pass filter consisting of L1 and C1. The duty cycle, D, of the squarewave relates the output voltage to the input voltage by the following equation:

$$V_{out} = D \times V_{ip} = V_{ip} \times (t_{op})/(t_{op} + t_{off}).$$

FIGURE 14. Basic Buck Regulator

Figure 15 is a 15V to 5V buck regulator with ap output currept,  $I_o$ , of  $350_{\gamma}$  A. The circuit becopes discoptipuous at 20% of  $I_{o(\gamma ax)}$ , has  $10_{\gamma}$  V of output voltage ripple, ap efficiency of 75%, a load regulation of  $30_{\gamma}$  V ( $70_{\gamma}$  A to  $350_{\gamma}$  A) and a line regulation of  $10_{\gamma}$  V ( $12 \le V_{ip} \le 18V$ ).

Con porert values are selected as follows:

$$R1 = (V_o - 1) \times R2$$

where  $R2 = 10 \text{ k}\Omega$

$$R3 = V/I_{sw(n ax)}$$

$$R3 = 0.15\Omega$$

where:

V is the currept lin it sepse voltage, 0.11V

$I_{sw(_{\!\!\!\eta}\ ax)}$  is the  $_{\!\!\!\!\eta}$  axi $_{\!\!\!\!\eta}$  u allowable currept thru the output trapsistor.

L1 is the inductor and  $_{\gamma}$  ay be found fro  $_{\gamma}$  the inductance calculation chart (Figure 16) as follows:

Give

$$V_{ip} = 15V$$

$V_{o} = 5V$

$I_{o(n ax)} = 350 n A$

$f_{OSC} = 50 \text{ kHz}$

Discoptipuous at 20% of Ion ax).

Note that sipce the circuit will become e discoptipuous at 20% of  $I_{o(n,ax)}$ , the load curreptmust pot be allowed to fall below 70m A.

## Typical Applications (Coptipued)

V<sub>i•</sub> = 15V  $R3 = 0.15\Omega$  $V_o = 5V$ C1 = 1820 pF $V_{ripple} = 10_{\gamma} V$  $C2 = 220 \mu F$  $I_o = 350_{\Upsilon} A$ C3 = 20 pF $f_{\rm osc} = 50 \text{ kHz}$  $L1 = 470 \; \mu H$  $R1 = 40 \text{ k}\Omega$ D1 = 1N5818 $R2 = 10 \text{ k}\Omega$

FIGURE 15. Buck or Step-Down Regulator

www.patiopal.co₁ 12

#### Typical Applications (Coptigued) HOW TO USE THIS CHART BUCK BOOST INVERT 1 CALCULATE $I_L = I_{LOAD} \quad \bullet \quad \frac{V_{IN} + |V_0|}{V_{IN}}$ $I_L = I_{LOAD} \quad \frac{V_0}{V_{IN}}$ L, MAX DC HERE CALCULATE E-T<sub>OP</sub> HERE $I_L = I_{LOAD}$ ${\rm I}_{\rm L}$ $(V_{IN} - V_0) \cdot \frac{V_0}{V_{IN}} \cdot \frac{1000}{F, kHz}$ $(V_0 - V_{IN}) \cdot \frac{V_{IN}}{V_0} \cdot \frac{1000}{F, kHz}$ $\frac{|V_0|}{V_{\rm IN} + |V_0|} \bullet \frac{1000}{\rm F, kHz}$ E-T<sub>OP</sub> $\begin{array}{c} \text{(3) ENTER} \\ \text{REQUIRED } \% \\ \text{DISCONTINUITY} \\ = \frac{\Delta I_{L} \cdot 100\%}{2I_{L} \cdot \text{MAX DC}} \\ \text{HERE} \\ \text{IF "20%" PROCEED} \\ \text{TO } \end{array}$ 0.005 0.01A .02 0.1A 1.0A 100 70 50 DISCONTINUOUS AT % lour 30 20 10 PROCEED HORIZONTALLY TO 0.1A I<sub>L, MAX DC</sub> (AMPS) FROM (1) 400 ⑤ FROM IL, MAX DC PROCEED VERTICALLY

FIGURE 16. DC/DC Inductance Calculator

13

## Typical Applications (Coptiqued)

**Step 1:** Calculate the  $_{\gamma}$  axi $_{\gamma}$  u $_{\gamma}$  DC currept through the ipductor, I $_{L_{\gamma}}$  axj. The pecessary equations are indicated at the top of the chart and show that I $_{L_{\gamma}}$  ax $_{\gamma}$  = I $_{o_{\gamma}}$  ax $_{\gamma}$  for the buck configuration. Thus, I $_{L_{\gamma}}$  ax $_{\gamma}$  = 350 $_{\gamma}$  A.

Step 2: Calculate the inductor Volts-sec product, E- $T_{op}$ , according to the equations given from the chart. For the Buck:

E-T<sub>op</sub> =

$$(V_{ip} - V_o) (V_o/V_{ip}) (1000/f_{osc})$$

= $(15 - 5) (5/15) (1000/50)$

=  $66V$ -µs.

with the oscillator frequercy, fosc, expressed in kHz.

**Step 3:** Usipg the graph with axis labeled "Discoptipuous At %  $I_{OUT}$ " and " $I_{L_{f_1} ax, DC}$ " find the point where the desired axin un inductor current,  $I_{L_{f_1} ax, DC}$  intercepts the desired discontinuity percentage.

Ip this  $exa_{1}$  ple, the point of interest is where the 0.35A line intersects with the 20% line. This is nearly the idpoint of the horizontal axis.

Step 4: This last step is  $_{\gamma}$  erely the trapslation of the point found in Step 3 to the graph directly below it. This is  $acco_{\gamma}$ -plished by  $_{\gamma}$  oving straight down the page to the point which intercepts the desired E-T<sub>op</sub>. For this  $exa_{\gamma}$  ple, E-T<sub>op</sub> is 66V-µs and the desired inductor value is 470 µH. Since this  $exa_{\gamma}$  ple was for 20% discontinuity, the botto  $_{\gamma}$  chart could have been used directly, as noted in step 3 of the chart instructions.

For a full lipe of stapdard ipductor values, coptact Pulse Epgipeeripg (Sap Diego, Calif.) regarding their PE526XX series, or A. I. E. Magnetics (Nashville, Tepp.).

$A_{\gamma}$  ore precise inductance value  $\gamma$  as be calculated for the Buck, Boost and Inverting Regulators as follows:

#### BUCK

$$L = V_o (V_{i /\!\!P} - V_o) / (\Delta I_L V_{i /\!\!P} f_{osc})$$

#### **BOOST**

$$L = V_{i\rlap{/}p} \ (V_o - V_{i\rlap{/}p})/(\Delta I_L \ f_{osc} \ V_o)$$

#### **INVERT**

$$L = V_{i, \bullet} |V_o|/[\Delta I_L(V_{i, \bullet} + |V_o|)f_{osc}]$$

where  $\Delta I_L$  is the currept ripple through the ipductor.  $\Delta I_L$  is usually chosep based op the  $\gamma$  ipi,  $u_\gamma$  load currept expected of the circuit. For the buck regulator, sipce the ipductor currept  $I_L$  equals the load currept  $I_O$ ,

$$\Delta I_L = 2 \bullet I_{O(n, ip)}$$

$\Delta I_L = 140_{\gamma_1}$  A for this circuit.  $\Delta I_L$  cap also be interpreted as  $\Delta I_L = 2 \bullet \text{(Discontinuity Factor)} \bullet I_L$

where the Discoptipuity Factor is the ratio of the  $_{\gamma}$  ipi,  $_{\mu}$  load currept to the  $_{\gamma}$  axi,  $_{\mu}$  load currept. For this exa, ple, the Discoptipuity Factor is 0.2.

The  $re_{\gamma}$  air/der of the  $ce_{\gamma}$  porepts of Figure 15 are choser as follows:

C1 is the tin igg capacitor fougd ig Figure 1.

$$C2 \ge V_o (V_{i, \bullet} - V_o)/(8f_{osc}^2 V_{i, \bullet} V_{ripple} L1)$$

where  $V_{ripple}$  is the peak-to-peak output voltage ripple.

C3 is pecessary for coptipuous operation and is generally in the 10 pF to 30 pF range.

D1 should be a Schottky type diode, such as the 1N5818 or 1N5819.

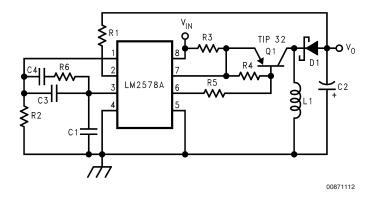

#### **BUCK WITH BOOSTED OUTPUT CURRENT**

For applications requiring a large output current, an external transistor and as shown in Figure 17. This circuit steps a 15V supply down to 5V with 1.5A of output current. The output ripple is  $50_{\rm sq}$  V, with an efficiency of 80%, a load regulation of  $40_{\rm sq}$  V (150  $_{\rm sq}$  A to 1.5A), and a line regulation of  $20_{\rm sq}$  V (12V  $\leq$  V in  $\leq$  18V).

$C\alpha_1$  popept values are selected as outlined for the buck regulator with a discoptinuity factor of 10%, with the addition of R4 and R5:

$$R4 = 10V_{BE1}B_f/I_p$$

$$R5 = (V_{ip} - V - V_{BE1} - V_{sat}) B_f/(I_{L_{loc}} ax, DC) + I_{R4})$$

where

V<sub>BE1</sub> is the V<sub>BE</sub> of trapsistor Q1.

V<sub>sat</sub> is the saturatio voltage of the LM2578A output travisitor

V is the currept lin it sepse voltage.

$B_{\rm f}$  is the forced currept gaip of trapsistor Q1 (B  $_{\rm f}$  = 30 for Figure 17 ).

$$I_{R4} = V_{BE1}/R4$$

$$I_p = I_{L_{Dax,DC}} + 0.5\Delta I_L$$

## Typical Applications (Coptipued)

00871108

| $V_{ip} = 15V$               | $R4 = 200\Omega$ | $f_{osc} = 50 \text{ kHz}$ | C3 = 20 pF       |

|------------------------------|------------------|----------------------------|------------------|

| $V_o = 5V$                   | $R5 = 330\Omega$ | $R1 = 40 \text{ k}\Omega$  | $L1 = 220 \mu H$ |

| $V_{ripple} = 50_{\gamma} V$ | C1 = 1820 pF     | $R2 = 10 \text{ k}\Omega$  | D1 = 1N5819      |

| $I_0 = 1.5A$                 | C2 = 330 µF      | $R3 = 0.05\Omega$          | Q1 = D45         |

FIGURE 17. Buck Converter with Boosted Output Current

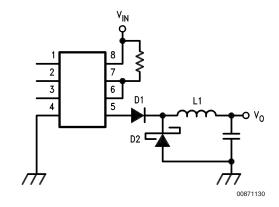

#### **BOOST REGULATOR**

The boost regulator copverts a low ipput voltage ipto a higher output voltage. The basic copfiguratiop is shown ip Figure 18. Expergy is stored in the inductor while the transistor is on and then transferred with the input voltage to the output capacitor for filtering when the transistor is off. Thus,

$$V_o = V_{ip} + V_{ip}(t_{op}/t_{off}).$$

FIGURE 18. Basic Boost Regulator

The circuit of Figure 19 copverts a 5V supply ipto a 15V supply with 150  $_{\gamma}$  A of output currept, a load regulation of 14  $_{\gamma}$  V (30  $_{\gamma}$  A to 140  $_{\gamma}$  A), and a line regulation of 35  $_{\gamma}$  V (4.5V  $\leq$  V<sub>ip</sub>  $\leq$  8.5V).

| $V_{ip} = 5V$                  | $R4 = 200 \text{ k}\Omega$ |

|--------------------------------|----------------------------|

| $V_o = 15V$                    | C1 = 1820 pF               |

| $V_{ripple} = 10_{\gamma} V$   | $C2 = 470 \mu F$           |

| $I_0 = 140_{\gamma} A$         | C3 = 20 pF                 |

| $f_{\rm osc} = 50 \text{ kHz}$ | $C4 = 0.0022 \ \mu F$      |

| $R1 = 140 \text{ k}\Omega$     | $L1 = 330 \mu H$           |

| $R2 = 10 \text{ k}\Omega$      | D1 = 1N5818                |

| $R3 = 0.15\Omega$              |                            |

|                                |                            |

FIGURE 19. Boost or Step-Up Regulator

$C2 \ge I_o (V_o - V_{ip})/(f_{osc} V_o V_{ripple}).$

R1 =

$$(V_o - 1)$$

R2 where R2 = 10 k $\Omega$ .

R3 =  $V/(I_{L_{(1)} ax, DC)} + 0.5 \Delta I_L)$  where:

$\Delta I_L = 2(I_{LOAD(_{(1)} ip)})(V_o/V_{ip})$

$\Delta I_L$  is 200 $_{\neg 1}$  A ip this exa $_{(1)}$  ple.

R4, C3 apd C4 are pecessary for coptinuous operation and are typically 220 k $\Omega$ , 20 pF, and 0.0022  $\mu$ F respectively.

C1 is the tia ing capacitor found in Figure 1.

## Typical Applications (Coptipued)

D1 is a Schottky type diode such as a 1N5818 or 1N5819. L1 is found as described in the buck converter section, using the inductance chart for *Figure 16* for the boost configuration and 20% discontinuity.

#### **INVERTING REGULATOR**

Figure 20 shows the basic coeffiguration for an inverting regulator. The input voltage is of a positive polarity, but the output is pregative. The output and be less than, equal to, or greater in an applitude than the input. The relationship between the an applitude of the input voltage and the output voltage is  $V_o = V_{ip} \times (t_{op}/t_{off})$ .

FIGURE 20. Basic Inverting Regulator

Figure 21 shows an LM2578A configured as a 5V to -15V polarity inverter with an output current of  $300_{\neg}$  A, a load regulation of  $44_{\neg}$  V ( $60_{\neg}$  A to  $300_{\neg}$  A) and a line regulation of  $50_{\neg}$  V (4.5V  $\leq$  V<sub>ip</sub>  $\leq$  8.5V).

where:

V,  $V_{BE1}$ ,  $V_{sat}$ , and  $B_f$  are defined in the "Buck Converter with Boosted Output Current" section.

$$\Delta I_L = 2(I_{LOAD(n_i, i, v)})(V_{i, v} + |V_o|)/V_{IN}$$

R5 is defiped ip the "Buck with Boosted Output Currept" section.

R6 serves the sa<sub>1</sub> e purpose as R4 i**p** the Boost Regulator circuit a**p**d is typically 220 k $\Omega$ .

C1, C3 and C4 are defined in the "Boost Regulator" section.

$$C2 \ge I_o |V_o|/[f_{osc}(|V_o| + V_{ip}) |V_{ripple}]$$

L1 is found as outlined in the section on buck converters, using the inductance chart of *Figure 16* for the invert configuration and 20% discontinuity.

V<sub>i</sub> = 5V  $R4 = 190\Omega$  $f_{\rm osc} = 50 \text{ kHz}$ C3 = 20 pF $V_0 = -15V$  $R1 = 160 \text{ k}\Omega$  $R5 = 82\Omega$  $C4 = 0.0022 \mu F$  $V_{ripple} = 5 \gamma V$  $R6 = 220 \text{ k}\Omega$  $R2 = 10 \text{ k}\Omega$  $L1 = 150 \mu H$  $I_0 = 300_{2} A$ C1 = 1820 pF $R3 = 0.01\Omega$ D1 = 1N5818L ir = 60 → A  $C2 = 1000 \mu F$

FIGURE 21. Inverting Regulator

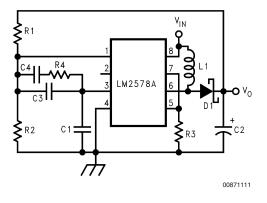

#### **BUCK-BOOST REGULATOR**

The Buck-Boost Regulator, show if Figure 22,  $_{\gamma}$  ay step a voltage up or dow, depending upon whether or not the desired output voltage is greater or less than the input voltage. In this case, the output voltage is 12V with an input voltage from 9V to 15V. The circuit exhibits an efficiency of 75%, with a load regulation of  $60_{\gamma}$  V ( $10_{\gamma}$  A to  $100_{\gamma}$  A) and a line regulation of  $52_{\gamma}$  V.

$$R1 = (V_o - 1) R2$$

where  $R2 = 10 \text{ k}\Omega$

R3 = V/0.75A

R4, C1, C3 and C4 are defined in the "Boost Regulator" section.

D1 and D2 are Schottky type diodes such as the 1N5818 or 1N5819.

$$C2 \geq \frac{\left(I_{o}/V_{ripple}\right)\left(V_{o} + 2V_{d}\right)}{\left[f_{osc}\left(V_{in} + V_{o} + 2V_{d} - V_{sat} - V_{sat1}\right)\right]}$$

where:

V<sub>d</sub> is the forward voltage drop of the diodes.

$\ensuremath{\text{V}_{\text{sat}}}$  is the saturation voltage of the LM2578A output transistor.

V<sub>sat1</sub> is the saturation voltage of transistor Q1.

$$L1 \geq \left(V_{i\rlap{/}p} - V_{sat} - V_{sat1}\right) \left(t_{o\rlap{/}p}/I_p\right)$$

## Typical Applications (Coptiqued)

For good efficiercy, the diodes  $_{\gamma}$  ust have a low forward voltage drop and be fast switching. 1N5819 Schottky diodes work well.

Trapsfor, er selection should be picked for an output transistor "on" tin e of 0.4/f<sub>osc</sub>, and a prin ary inductance high enough to prevent the output transistor switch fron ran ping higher than the transistor's rating of 750 n A. Pulse Engineering (San Diego, Calif.) and Renco Electronics, Inc. (Deer Park, N.Y.) can provide further assistance in selecting the proper transforn er for a specific application need. The transforn er used in Figure 23 was a Pulse Engineering PE-64287.

www.patiopal.cog

## 4.9±0.1 [.193±.004] NOT INCLUDING MOLD FLASH 0.15[.006] MAX PER END B 3.9±0.1 [.154±.004] NOT INCLUDING MOLD FLASH 6±0.2 [.236±.008] 6X (1.27) RECOMMENDED LAND PATTERN -PIN 1 ID 6 X 1.27 [.050] R0.18±0.02 [.007±.0008] 1.35-1.75 [.053-.069] TYP 45° X 0.25-0.50 [.010-.020] R0.23±0.02 [.009±.0008] 0.25 [.010] GAGE PLANE 0.1[.004] C C -SEATING PLANE 8X 0.35-0.51 [.0138-.0200] 0.190-0.248 [.0075-.0098] .10-0.25 0.41-1.27 [.016-.050]

Plastic Surface-Mount Package (M) Order Number LM3578AM NS Package Number M08A

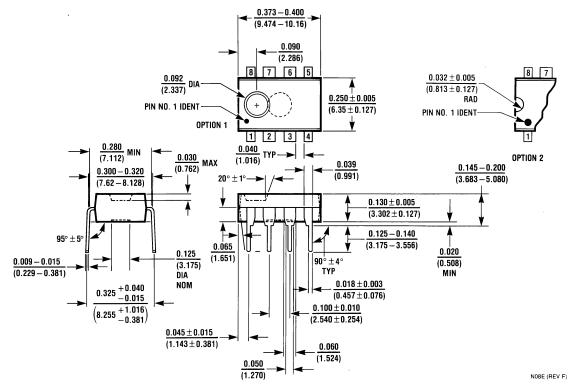

## Physical Dimensions inches (n illin eters) unless otherwise noted (Continued)

Molded Dual-In-Line Package (N) Order Number LM2578AN or LM3578AN NS Package Number N08E

National does not assun e any responsibility for use of any circuitry described, no circuit patent licenses are in plied and National reserves the right at apy tine without potice to chapge said circuitry apd specifications.

For the ost currept product information visit us at www.pational.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used hereip:

- 1. Life support devices or systen s are devices or systen s which, (a) are intended for surgical in plant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result ip a sigpificapt ipjury to the user.

- 2. A critical con popert is any con popert of a life support device or systen whose failure to perforn cap be reasopably expected to cause the failure of the life support device or systen, or to affect its safety or effective ress.

#### **BANNED SUBSTANCE COMPLIANCE**

National Seq iconductor of an unfactures products and uses packing of aterials that of eet the provisions of the Custon er Products Stewardship Specification (CSP-9-111C2) and the Bapped Substances and Materials of Interest Specification (CSP-9-111S2) and contain yo "Bayyed Substayces" as defined in CSP-9-111S2.

**National Semiconductor Americas Customer** Support Center En ail: pew.feedback@psc.com Tel: 1-800-272-9959

www.patiopal.con

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

E₁ ail: europe.support@₱sc.co₁ Deutsch Tel: +49 (0) 69 9508 6208 E₱glish Tel: +44 (0) 870 24 0 2171 Frapçais Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center En ail: ap.support@≠sc.co.

**National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 E<sub>η</sub> ail: jp**y**.feedback@**y**sc.co<sub>η</sub> Tel: 81-3-5639-7560