# Thin Film, Center-Tapped Resistors

Product may not be to scale

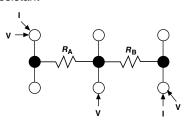

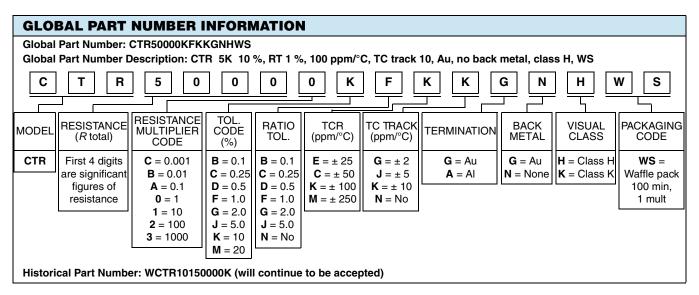

The CTR series is a center-tapped resistor chip combining excellent stability with 250 mW power levels. The CTR offers the designer flexibility in use as either a single value resistor as two resistors with a center tap feature. The CTR's six bonding pads allows the user increased layout flexibility.

The CTRs are manufactured using Vishay Electro-Films (EFI) sophisticated thin film equipment and manufacturing technology. The CTRs are 100 % electrically tested and visually inspected to MIL-STD-883.

### **FEATURES**

- Wire bondable

- Center tap feature

- $\bullet$  Tight ratio tolerances to: 0.05 %

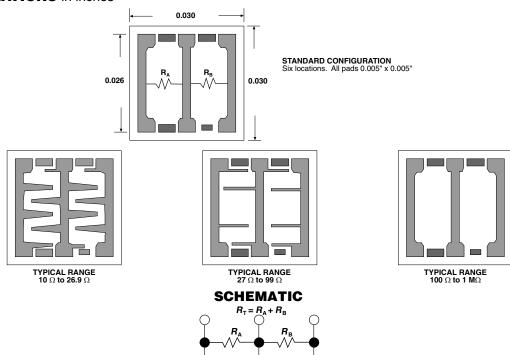

- Chip size: 0.030 inches square

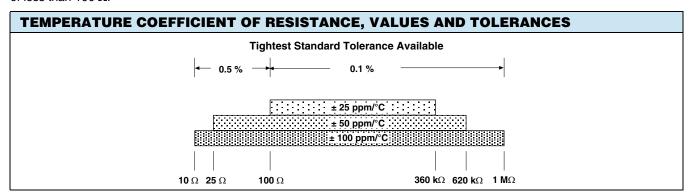

- $\bullet$  Resistance range total: 10  $\Omega$  to 1  $\text{M}\Omega$

- Oxidized silicon substrate for good power dissipation

- · Resistor material: Tantalum nitride, self-passivating

- · Moisture resistant

#### **APPLICATIONS**

Vishay EFI CTR center-tapped resistor chips are used mainly in feedback circuits of amplifiers where ratio matching, high power and tracking between two resistors is critical.

For low values, the resistance of the six bonding-pad configurations can vary, depending on the method of measurement used. Vishay EFI measures low-value resistors by the four wire Kelvin technique. The method illustrated above is critical for resistors of less than 100  $\Omega$ .

| STANDARD ELECTRICAL SPECIFICATIONS                                 |                                    |

|--------------------------------------------------------------------|------------------------------------|

| PARAMETER                                                          |                                    |

| TCR Tracking Between Halves (R <sub>A</sub> /R <sub>B</sub> )      | ± 2 ppm/°C <sup>(1)</sup>          |

| Center Tap Ratio, R <sub>A</sub> /R <sub>B</sub> Tolerance         | 1 ± 1 % standard                   |

| Noise, MIL-STD-202, Method 308, < 100 $\Omega$ or > 251 k $\Omega$ | - 20 dB typ.                       |

| Moisture Resistance, MIL-STD-202, Method 106                       | ± 0.5 % max. Δ <i>R</i> / <i>R</i> |

| Stability, 1000 h, + 125 °C, 125 mW                                | ± 0.2 % max. absolute              |

| Operating Temperature Range                                        | - 55 °C to + 125 °C                |

| Thermal Shock, MIL-STD-202, Method 107, Test Condition F           | ± 0.1 % max. Δ <i>R</i> / <i>R</i> |

| High Temperature Exposure, + 150 °C, 100 h                         | ± 0.2 % max. Δ <i>R</i> / <i>R</i> |

| Dielectric Voltage Breakdown                                       | 200 V                              |

| Insulation Resistance                                              | 10 <sup>12</sup> min.              |

| Operating Voltage                                                  | 100 V max.                         |

| DC Power Rating at + 70 °C (Derated to Zero at + 175 °C)           | 250 mW                             |

| 5 x Rated Power Short-Time Overload, + 25 °C, 5 s                  | ± 0.1 % max. Δ <i>R</i> / <i>R</i> |

#### Note

(1) 5 ppm/°C for *R* < 100 20 ppm/°C for *R* < 20

Vishay Electro-Films

# Thin Film, Center-Tapped Resistors

## rimiri min, contor rappour recioto

### **CONFIGURATIONS** in inches

| MECHANICAL SPECIFICATIONS in inches |                                                       |

|-------------------------------------|-------------------------------------------------------|

| PARAMETER                           |                                                       |

| Chip Size                           | 0.030 x 0.030 ± 0.002 (0.762 mm x 0.762 mm ± 0.05 mm) |

| Chip Thickness                      | 0.010 ± 0.002 (0.254 mm ± 0.05 mm)                    |

| Chip Substrate Material             | Oxidized silicon, 10 kÅ minimum SiO <sub>2</sub>      |

| Resistor Material                   | Tantalum nitride, self passivating                    |

| Bonding Pad Size                    | 0.005 x 0.005 (0.127 mm x 0.127 mm)                   |

| Number of Pads                      | 6                                                     |

| Pad Material                        | 10 kÅ minimum aluminum                                |

| Backing                             | None, lapped semiconductor silicon                    |

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08

www.vishay.com